|

|

PDF SI598 Data sheet ( Hoja de datos )

| Número de pieza | SI598 | |

| Descripción | 10-810MHZ I2C PROGRAMMABLE XO/VCXO | |

| Fabricantes | Silicon Laboratories | |

| Logotipo | ||

Hay una vista previa y un enlace de descarga de SI598 (archivo pdf) en la parte inferior de esta página. Total 28 Páginas | ||

|

No Preview Available !

Si598/Si599

1 0 – 8 1 0 M H Z I 2C P ROGRAMMABLE X O / V C X O

Features

I2C programmable output

frequencies from 10 to 810 MHz

0.5 ps RMS phase jitter

Superior power supply rejection:

0.3–0.4 ps additive jitter

Available LVPECL, CMOS, LVDS,

and CML outputs

1.8, 2.5, or 3.3 V supply

Pin- and register-compatible with

Si570/571

Programmable with 28 parts per

trillion frequency resolution

Integrated crystal provides stability

and low phase noise

Frequency changes up to

±3500 ppm are glitchless

–40 to 85 °C operation

Industry-standard 5x7 mm package

Applications

SONET / SDH / xDSL

Ethernet / Fibre Channel

3G SDI / HD SDI

Multi-rate PLLs

Multi-rate reference clocks

Description

Frequency margining

Digital PLLs

CPU / FPGA FIFO control

Adaptive synchronization

Agile RF local oscillators

The Si598 XO/Si599 VCXO utilizes Silicon Laboratories' advanced DSPLL®

circuitry to provide a low-jitter clock at any frequency. They are user-

programmable to any output frequency from 10 to 810 MHz with 28 parts per

trillion (PPT) resolution. The device is programmed via a 2-pin I2C compatible

serial interface. The wide frequency range and ultra-fine programming resolution

make these devices ideal for applications that require in-circuit dynamic frequency

adjustments or multi-rate operation with non-integer related rates. Using an

integrated crystal, these devices provide stable low jitter frequency synthesis and

replace multiple XOs, clock generators, and DAC controlled VCXOs.

Functional Block Diagram

OE

Vc

(Si599)

VDD

Power Supply Filtering

Fixed

Frequency

Oscillator

ADC

Any Frequency

DSPLL®

10 to 810 MHz

Clock Synthesis

I2C Interface

SDA

SCL

GND

CLK+

CLK–

Si5602

Ordering Information:

See page 22.

Pin Assignments:

See page 21.

(Top View)

SDA

NC 1

7

6

VDD

OE 2

5 CLK–

GND 3

4 CLK+

8

SCL

Si598

VC 1

SDA

7

6 VDD

OE 2

5 CLK–

GND 3

4

8

SCL

Si599

CLK+

Rev. 1.0 11/11

Copyright © 2011 by Silicon Laboratories

Si598/Si599

1 page

Si598/Si599

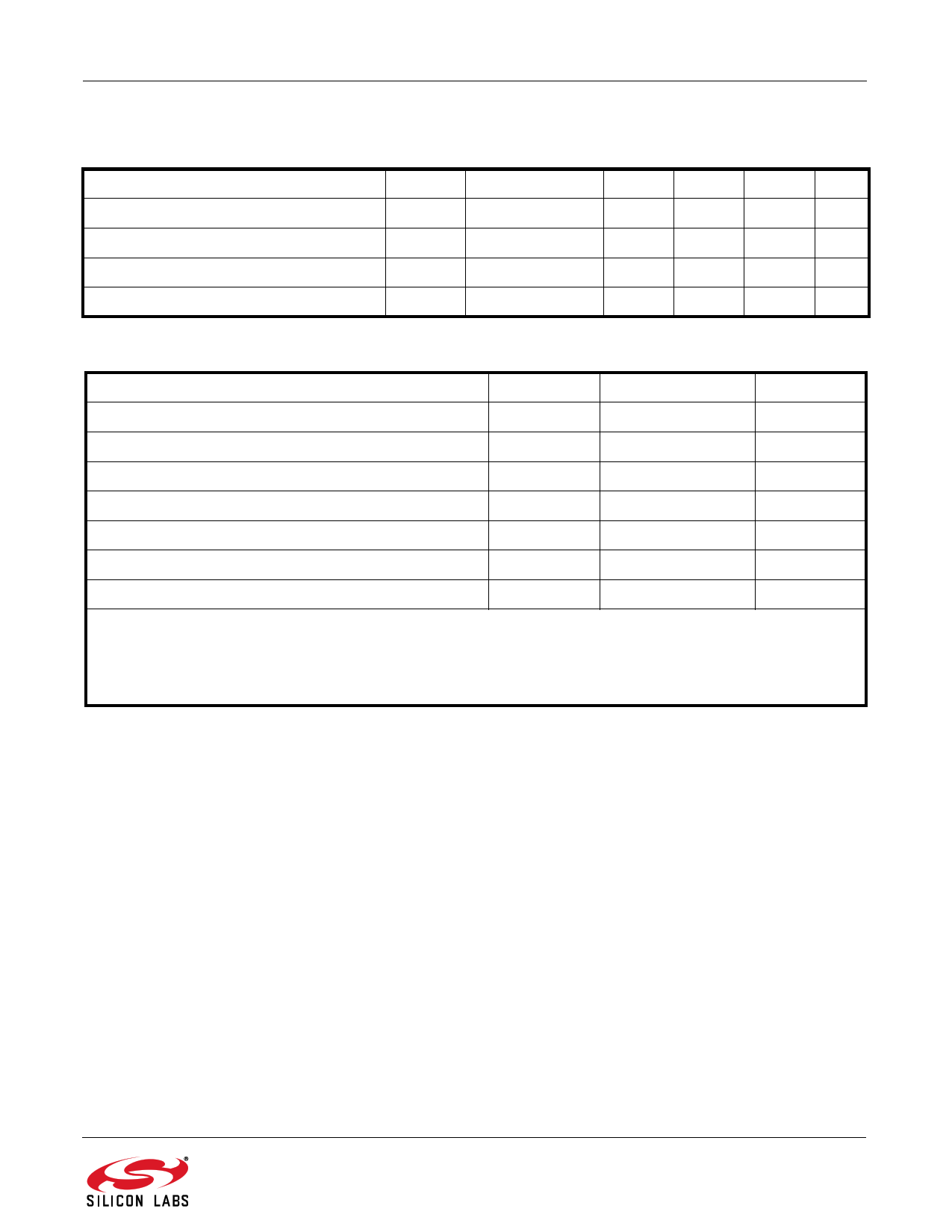

2. Electrical Specifications

Table 1. Recommended Operating Conditions

Parameter

Symbol Test Condition Min Typ Max Units

3.3 V option

2.97

3.3

3.63

V

Supply Voltage1

VDD 2.5 V option

1.8 V option

2.25

1.71

2.5

2.75

V

1.8

1.89

V

Supply Current

Output enabled

LVPECL

— 120 130 mA

IDD

CML

LVDS

— 108 120 mA

— 99 110 mA

CMOS

— 90 100 mA

Output Enable (OE)2,

Serial Data (SDA),

Serial Clock (SCL)

Tristate mode

VIH

VIL

—

0.75 x VDD

—

60

—

—

75 mA

—V

0.5 V

Operating Temperature Range

TA

–40 — 85 ºC

Notes:

1. Selectable parameter specified by part number. See Section 7. Ordering Information on page 22 for further details.

2. OE pin includes a 17 k pullup resistor to VDD for OE Active High Option. OE pin includes 17 kpull down for OE

Active Low. See Section “7.Ordering Information”.

Table 2. VC Control Voltage Input (Si599)

(Typical values TA = 25 ºC, VDD = 3.3 V, min/max limits VDD = 1.8 ±5%, 2.5 or 3.3 V ±10%, TA = –40 to 85 ºC unless otherwise

noted)

Parameter

Symbol Test Condition

Min

Typ

Max Units

Control Voltage Tuning Slope1,2,3

KV

10 to 90% of VDD

—

45

— ppm/V

— 95 — ppm/V

— 125 — ppm/V

— 185 — ppm/V

— 380 — ppm/V

Control Voltage Linearity4

LVC

BSL

–5 ±1 +5 %

Incremental

–10 ±5 +10 %

Modulation Bandwidth

BW

9.3

10.0

10.7

kHz

VC Input Impedance

VC Input Capacitance

Nominal Control Voltage

Control Voltage Tuning Range

ZVC

CVC

VCNOM

VC

@ fO

500 —

— k

— 50 — pF

— VDD/2 —

V

0

—

VDD

V

Notes:

1. Positive slope; selectable option by part number. See 7. Ordering Information on page 22.

2. For best jitter and phase noise performance, always choose the smallest KV that meets the application’s minimum APR

requirements. See “AN266: VCXO Tuning Slope (KV), Stability, and Absolute Pull Range (APR)” for more information.

3. KV variation is ±10% of typical values.

4. BSL determined from deviation from best straight line fit with VC ranging from 10 to 90% of VDD. Incremental slope

determined with VC ranging from 10 to 90% of VDD.

Rev. 1.0

5

5 Page

Si598/Si599

Table 13. Thermal Characteristics

(Typical values TA = 25 ºC, VDD = 3.3 V)

Parameter

Symbol Test Condition Min Typ Max Unit

Thermal Resistance Junction to Ambient

Thermal Resistance Junction to Case

JA

JC

Still Air

Still Air

— 84.6 — °C/W

— 38.8 — °C/W

Ambient Temperature

Junction Temperature

TA

TJ

–40 —

85 °C

— — 125 °C

Table 14. Absolute Maximum Ratings

Parameter

Symbol

Rating

Units

Supply Voltage, 1.8 V Option

Supply Voltage, 2.5/3.3 V Option

Input Voltage

Storage Temperature

ESD Sensitivity (HBM, per JESD22-A114)

VDD

VDD

VI

TS

ESD

–0.5 to +1.9

–0.5 to +3.8

–0.5 to VDD + 0.3

–55 to +125

2000

V

V

V

ºC

V

Soldering Temperature (lead-free profile)

Soldering Temperature Time @ TPEAK (lead-free profile)

TPEAK

tP

260

20–40

ºC

seconds

Notes:

1. Stresses beyond the absolute maximum ratings may cause permanent damage to the device. Functional operation or

specification compliance is not implied at these conditions.

2. The device is compliant with JEDEC J-STD-020C. Refer to Si5xx Packaging FAQ available for download at

www.silabs.com/VCXO for further information, including soldering profiles.

Rev. 1.0

11

11 Page | ||

| Páginas | Total 28 Páginas | |

| PDF Descargar | [ Datasheet SI598.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| SI590 | (SI590 / SI591) 1 ps MAX JITTER CRYSTAL OSCILLATOR | Silicon Laboratories |

| SI5902BDC | Dual N-Channel 30 V (D-S) MOSFET | Vishay Siliconix |

| SI5902DC | Dual N-Channel 30-V (D-S) MOSFET | Vishay Siliconix |

| SI5903DC | Dual P-Channel 2.5-V (G-S) MOSFET | Vishay Siliconix |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |