|

|

PDF SI595 Data sheet ( Hoja de datos )

| Número de pieza | SI595 | |

| Descripción | VOLTAGE-CONTROLLED CRYSTAL OSCILLATOR (VCXO) | |

| Fabricantes | Silicon Laboratories | |

| Logotipo | ||

Hay una vista previa y un enlace de descarga de SI595 (archivo pdf) en la parte inferior de esta página. Total 12 Páginas | ||

|

No Preview Available !

Si595

REVISION D

VOLTAGE-CONTROLLED CRYSTAL OSCILLATOR (VCXO)

10 TO 810 MHZ

Features

Available with any-rate output

frequencies from 10 to 810 MHz

3rd generation DSPLL® with

superior jitter performance

Internal fixed fundamental mode

crystal frequency ensures high

reliability and low aging

Available CMOS, LVPECL,

LVDS, and CML outputs

3.3, 2.5, and 1.8 V supply options

Industry-standard 5 x 7 mm

package and pinout

Pb-free/RoHS-compliant

–40 to +85 ºC operating range

Applications

SONET/SDH (OC-3/12/48) FTTx

Networking

Clock recovery and jitter cleanup PLLs

SD/HD SDI/3G SDI video FPGA/ASIC clock generation

Description

The Si595 VCXO utilizes Silicon Laboratories’ advanced DSPLL® circuitry to

provide a low-jitter clock at high frequencies. The Si595 is available with

any-rate output frequency from 10 to 810 MHz. Unlike traditional VCXOs,

where a different crystal is required for each output frequency, the Si595

uses one fixed crystal to provide a wide range of output frequencies. This IC-

based approach allows the crystal resonator to provide exceptional

frequency stability and reliability. In addition, DSPLL clock synthesis

provides supply noise rejection, simplifying the task of generating low-jitter

clocks in noisy environments. The Si595 IC-based VCXO is factory-

configurable for a wide variety of user specifications including frequency,

supply voltage, output format, tuning slope, and absolute pull range (APR).

Specific configurations are factory programmed at time of shipment, thereby

eliminating the long lead times associated with custom oscillators.

Functional Block Diagram

VDD CLK– CLK+

Si5602

Ordering Information:

See page 7.

Pin Assignments:

See page 6.

(Top View)

VC 1

OE 2

GND 3

6 VDD

5 CLK–

4 CLK+

Fixed

Frequency

XO

Any-rate

10–810 MHz

DSPLL®

Clock Synthesis

ADC

Vc

OE

GND

Rev. 1.2 4/13

Copyright © 2013 by Silicon Laboratories

Si595

1 page

Si595

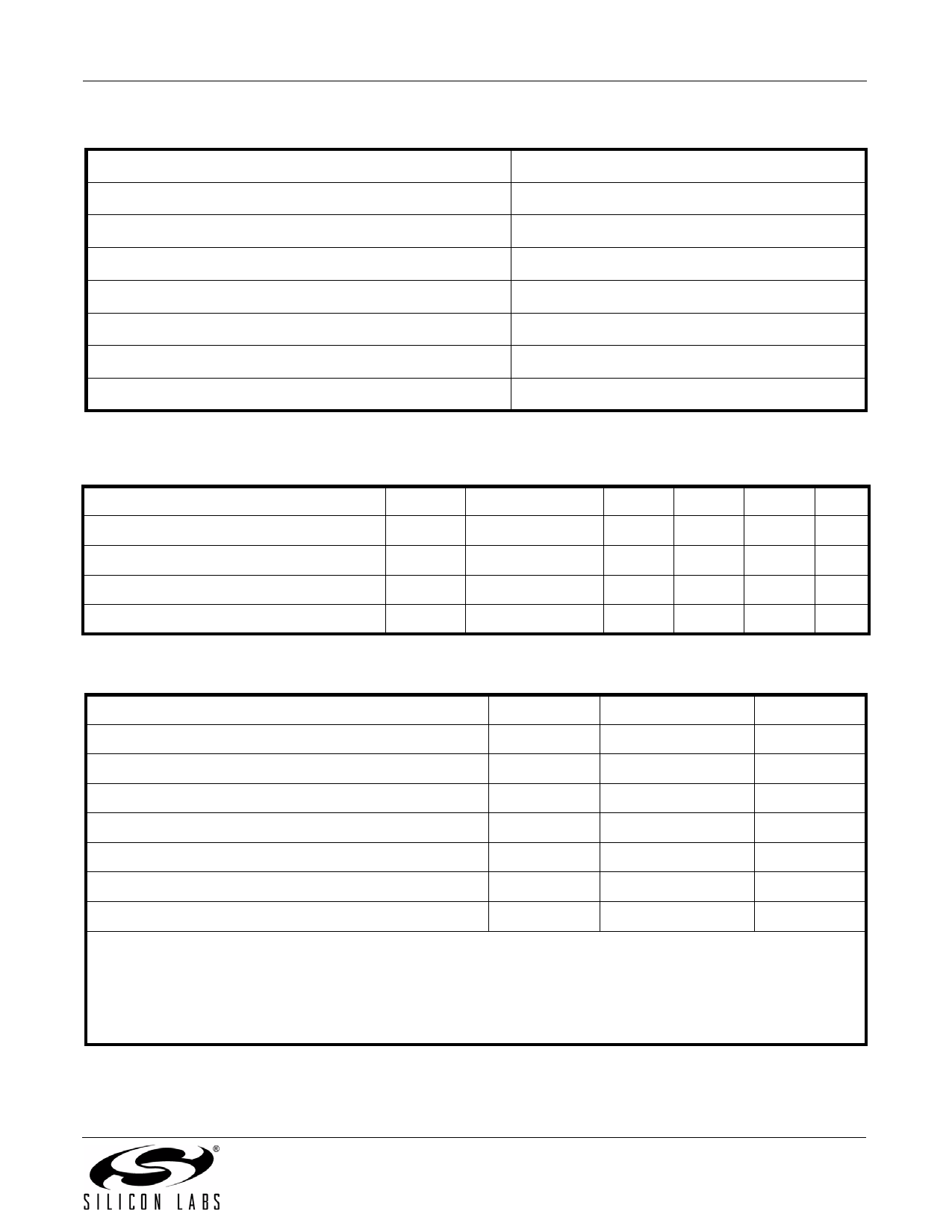

Table 8. Environmental Compliance and Package Information

Parameter

Conditions/Test Method

Mechanical Shock

Mechanical Vibration

Solderability

Gross and Fine Leak

Resistance to Solder Heat

Moisture Sensitivity Level

MIL-STD-883, Method 2002

MIL-STD-883, Method 2007

MIL-STD-883, Method 2003

MIL-STD-883, Method 1014

MIL-STD-883, Method 2036

J-STD-020, MSL1

Contact Pads

Gold over Nickel

Table 9. Thermal Characteristics

(Typical values TA = 25 ºC, VDD = 3.3 V)

Parameter

Symbol Test Condition Min Typ Max Unit

Thermal Resistance Junction to Ambient

Thermal Resistance Junction to Case

Ambient Temperature

Junction Temperature

JA

JC

TA

TJ

Still Air

Still Air

— 84.6 — °C/W

— 38.8 — °C/W

–40 —

85 °C

— — 125 °C

Table 10. Absolute Maximum Ratings1

Parameter

Symbol

Rating

Units

Maximum Operating Temperature

TAMAX

85

ºC

Supply Voltage

VDD –0.5 to +3.8

V

Input Voltage

VI –0.5 to VDD + 0.3

Storage Temperature

TS –55 to +125 ºC

ESD Sensitivity (HBM, per JESD22-A114)

ESD

2500

V

Soldering Temperature (Pb-free profile)2

Soldering Temperature Time @ TPEAK (Pb-free profile)2

TPEAK

tP

260

20–40

ºC

seconds

Notes:

1. Stresses beyond those listed in Absolute Maximum Ratings may cause permanent damage to the device. Functional

operation or specification compliance is not implied at these conditions. Exposure to maximum rating conditions for

extended periods may affect device reliability.

2. The device is compliant with JEDEC J-STD-020C. Refer to Si5xx Packaging FAQ available for download from

www.silabs.com/VCXO for further information, including soldering profiles.

Rev. 1.2

5

5 Page

DOCUMENT CHANGE LIST:

Revision 0.1 to Revision 0.2

Updated Table 5, “CLK± Output Phase Jitter,” on

page 4.

Updated typical phase jitter from 0.6 to 0.7 ps for

kV = 380 ppm/V.

Revision 0.2 to Revision 1.0

Updated 2.5 V/3.3 V and 1.8 V CML output level

specifications in Table 4 on page 3.

Updated Si595 device to support frequencies up to

810 MHz for LVPECL, LVDS, and CML outputs.

Separated 1.8 V, 2.5 V/3.3 V supply voltage.

specifications for CML output in Table 3 on page 5.

Updated Note 1 of Table 5 on page 4 to refer to

AN256.

Updated Table 8 on page 5 to include the "Moisture

Sensitivity Level" and "Contact Pads" rows.

Updated Figure 3 and Table 13 on page 9 to reflect

specific marking information.

Revision 1.0 to Revision 1.1

Swapped D and E values in Table 12 on page 8.

Revision 1.1 to Revision 1.2

Added Table 9, “Thermal Characteristics,” on

page 5.

Si595

Rev. 1.2

11

11 Page | ||

| Páginas | Total 12 Páginas | |

| PDF Descargar | [ Datasheet SI595.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| SI590 | (SI590 / SI591) 1 ps MAX JITTER CRYSTAL OSCILLATOR | Silicon Laboratories |

| SI5902BDC | Dual N-Channel 30 V (D-S) MOSFET | Vishay Siliconix |

| SI5902DC | Dual N-Channel 30-V (D-S) MOSFET | Vishay Siliconix |

| SI5903DC | Dual P-Channel 2.5-V (G-S) MOSFET | Vishay Siliconix |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |