|

|

PDF MT3332 Data sheet ( Hoja de datos )

| Número de pieza | MT3332 | |

| Descripción | GNSS Host-Based Solution Technical Brief | |

| Fabricantes | MEDIATEK | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de MT3332 (archivo pdf) en la parte inferior de esta página. Total 24 Páginas | ||

|

No Preview Available !

MT3332 GNSS Host-Based Solution

Technical Brief

Version:

Release date:

1.0

September 8, 2014

Specifications are subject to change without notice.

© 2014 MediaTek Inc.

This document contains information that is proprietary to MediaTek Inc.

Unauthorized reproduction of this information in whole or in part is strictly prohibited.

1 page

MT3332

GNSS Host-Based Solution Technical Brief

1.2 Features

• Specifications

o GPS/GLONASS/GALILEO/BEID

OU (after ICD released) receiver

o Supports multi-GNSS incl. QZSS,

SBAS ranging

o Supports

WAAS/EGNOS/MSAS/GAGAN

o 12 multi-tone active interference

cancellers (ISSCC2011 award)

o RTCM ready

o Indoor and outdoor multi-path

detection and compensation

o Supports FCC E911 compliance

and A-GPS

o Max. fixed update rate up to 5 Hz

• Advanced software features

o AlwaysLocateTM advanced location

awareness technology

o EPOTM/HotStillTM orbit prediction

• Reference oscillator

o TCXO

Frequency: 16.368 MHz,

12.6 ~ 40.0 MHz

Frequency variation: ±2.5

ppm

o Crystal

Frequency: 26 MHz, 12.6

~ 40.0 MHz

Frequency accuracy: ±10

ppm

• RF configuration

o SoC, integrated in single chip with

CMOS process

• Pulse-per-second (PPS) GPS time

reference

o Adjustable duty cycle

o Typical accuracy: ±10 ns

• Power scheme

o A 1.8 volts SMPS build-in SOC

o Direct lithium battery connection

(2.8 ~ 4.3 volts)

o Self build 1.1 volts RTC LDO, 1.1

volts core LDO, and 2.8 volts

TCXO LDO

• Build-in reset controller

o Does not need of external reset

control IC

• Internal real-time clock (RTC)

o 32.768 KHz ± 20 ppm crystal

o 1.1 volts RTC clock output

o Supports external pin to wake up

MT3332

• Backup mode

o A Force_On pin to ease backup

mode application circuit.

• Serial interface

o 3 UARTs

o SPI

o I2C

o GPIO interface (up to 15 pins)

• NMEA

o NMEA 0183 standard V3.01 and

backward compliance

o Supports 219 different data

• Superior sensitivities

o Acquisition: -148 dBm (cold) /

-163 dBm (hot)

o Tracking: -165 dBm

• Ultra-low power consumption

(GPS+GLONASS)

© 2014 MediaTek Inc.

Page 5 of 24

This document contains information that is proprietary to MediaTek Inc.

Unauthorized reproduction or disclosure of this information in whole or in part is strictly prohibited.

M

5 Page

MT3332

GNSS Host-Based Solution Technical Brief

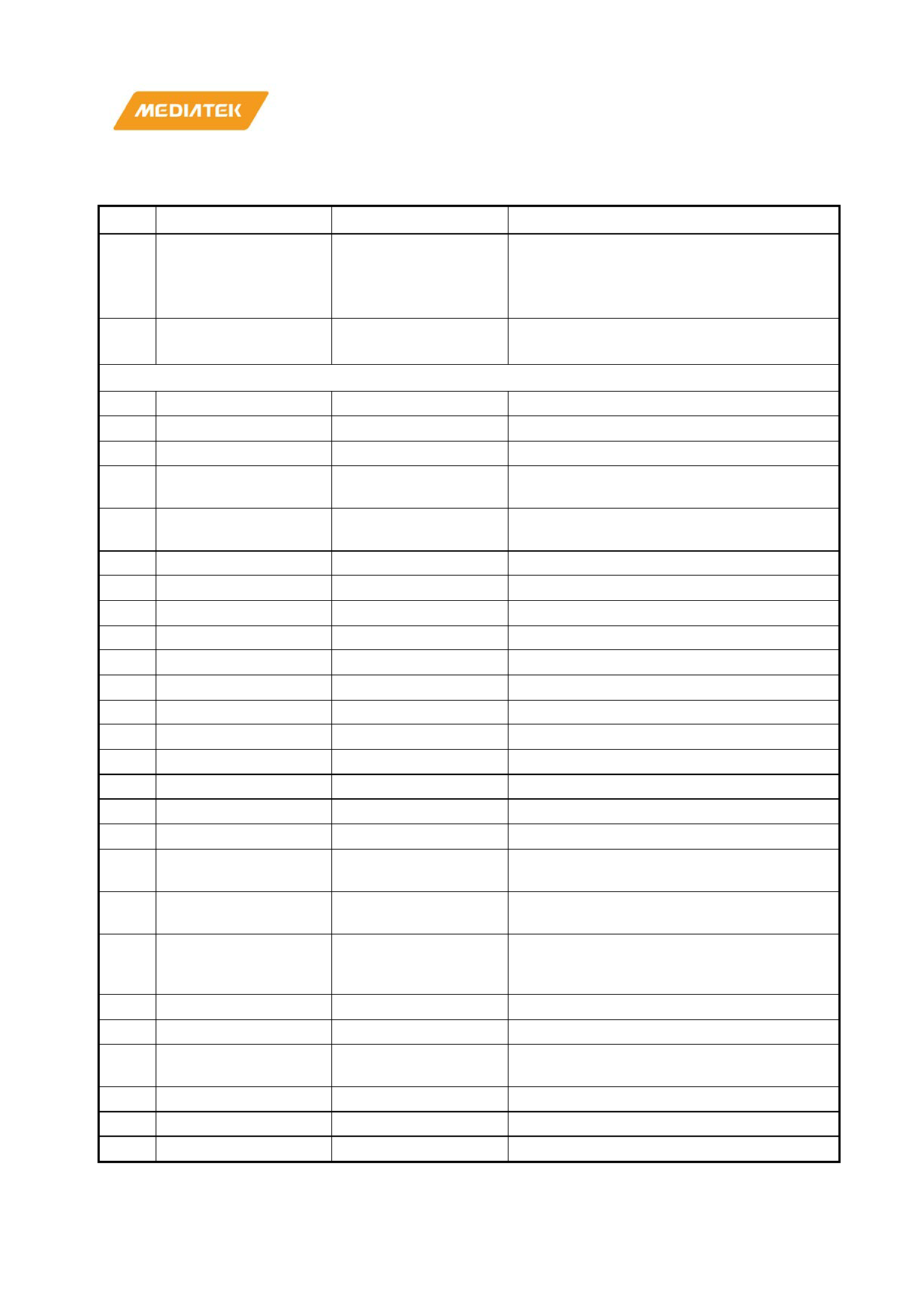

Pin# Symbol

23 32K_OUT/DR_IN

22 FORCE_ON

RF & analog

1 AVDD18_RXFE

2 T1P

3 T1N

A2/B2/

C2/D2

AVSS_RF

4 AVDD18_CM

5 OSC

48 RF_IN

6 DVDD11_CORE1

24 DVDD11_CORE2

43 DVDD11_CORE3

DVSS11_CORE

30 DVDD28_IO1

42 DVDD28_IO2

29 GND

DVSS28_IO

DVDD28_SF

DVSS28_SF

7 VREF

8 AVSS43_MISC

9 AVDD43_VBAT

10 AVDD_TCXO_SW

11 AVDD28_TLDO

12 AVDD28_CLDO

13 AVDD11_CLDO

AVSS11_CLDO

14 AVSS43_DCV

Type

Description

1.1V LVTTL I/O

PPU, PPD, SMT

4mA, 8mA, 12mA, 16mA

PDR

RTC domain GPIO pin, can be programmed to be

32KHz clock output or DR wake-up signal input

Default: pull-down

Default: 16mA driving

1.1V LVTTL input

PPU,PPD, SMT

Logic high to force power on this chip.

Default: pull-up

RF power

Analog signal

Analog signal

RF ground

RF power

Analog signal

RF signal

Digital power

Digital power

Digital power

Digital ground

Digital power

Digital power

Digital ground

Digital ground

Digital power

Digital ground

Analog

Analog ground

Analog power

Analog power

Analog power

Analog power

Analog power

Analog ground

SMPS

1.8V supply for RF core circuits

RF testing signal

RF testing signal

RF ground pins

1.8V supply for XTAL OSC, bandgap, thermal

sensor and level shifter

Input for crystal oscillator or TCXO

LNA RF Input pin

Digital 1.1V core power input

Digital 1.1V core power input

Digital 1.1V core power input

Digital 1.1V core ground

Digital 1.8/2.8V IO power input

Digital 1.8/2.8V IO power input

Digital ground

Digital 1.8/2.8V IO ground

Digital 2.8V serial flash power input

Digital 2.8V serial flash ground

Bandgap output pin. Must add 1uF decoupling cap

on EVB.

GND pin for buck controller, TCXO LDO and

start-up block

TCXO LDO input pin. Always be powered by

external source. UVLO will detect this PIN to

check power status.

TCXO power switch output pin

TCXO LDO output pin

Core LDO input pin. Always powered by external

source or SMPS

Core LDO output pin

GND pin for core LDO

SMPS GND pin

© 2014 MediaTek Inc.

Page 11 of 24

This document contains information that is proprietary to MediaTek Inc.

Unauthorized reproduction or disclosure of this information in whole or in part is strictly prohibited.

11 Page | ||

| Páginas | Total 24 Páginas | |

| PDF Descargar | [ Datasheet MT3332.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| MT3332 | GNSS Host-Based Solution Technical Brief | MEDIATEK |

| MT3337 | GPS All-in-One Solution | MEDIATEK |

| MT3339 | GPS All-in-One Solution | MEDIATEK |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |