|

|

PDF TLG1100 Data sheet ( Hoja de datos )

| Número de pieza | TLG1100 | |

| Descripción | Ultra-Low Power NTSC/PAL TV-On-Chip | |

| Fabricantes | Telegent Systems | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de TLG1100 (archivo pdf) en la parte inferior de esta página. Total 15 Páginas | ||

|

No Preview Available !

TLG1100

Ultra-Low Power NTSC/PAL TV-On-Chip

Description

The TLG1100 is a high performance, ultra-low

power RF tuner combined with an NTSC/PAL

compatible video decoder on a single chip. The

TLG1100 is a true single-chip design, requiring

no external SAW or ceramic filters to achieve full

channel selectivity with an average power

consumption is only 250 mW. Capable of

receiving any channel from 50 to 800 MHz,

designs employing the TLG1100 can be

deployed for analog television reception nearly

worldwide with only minimal software changes.

The TLG1100 utilizes a direct-conversion, zero-

IF architecture that allows for extremely good

image and adjacent channel signal rejection. A

wideband, low-noise amplifier is used to receive

the entire video signal band from the antenna,

and provides a gain range in excess of 60 dB. A

single down conversion I/Q mixer then translates

the desired channel to DC.

At baseband, an anti-aliasing filter is combined

with a second 60 dB variable-gain amplifier to

provide the first level of adjacent-channel

rejection, as well as provide signal conditioning

for interfacing into the dual 10-bit analog-to-

digital converters. Subsequent processing by the

DSP provides final adjacent-channel rejection

and audio/video carrier demodulation. The audio

stream is FM-demodulated and passed to the

audio output port, whereas the CVBS video

stream is separated into component video and

output onto the video data bus.

Telegent Systems’ SureTrak™ DSP-based tuner

architecture enables several unique features in

the decoder that make it ideal for the mobile

reception environment. Unlike conventional

analog decoders, the TLG1100 can compensate

for multi-path fading thereby preventing severe

ghosting and picture degradation when the

receiving antenna is small and in-motion. In

addition, if momentary signal dropout is

detected, the TLG1100 can be programmed to

hold the prior frame, preventing severe breakup

in the perceived image. For high-speed motion

applications, the SureTrak™ architecture

provides automatic Doppler compensation for

time-varying frequency shifts as high as 50 Hz.

The output of the video decoder is an 8-bit

parallel component video stream interface

compliant with CCIR/ITU 601; video timing is

entirely generated internally. Also, an adaptive

2D comb filter is available for enhanced color

fidelity on larger displays. Both analog and

digital audio (I2S) is supported. All configuration

control and register access is done via a 2-wire

(I2C-compliant) serial port.

As an additional feature, the TLG1100 directly

supports worldwide FM radio reception without

requiring any additional components.

Features

• Fully integrated, single-chip tuner

plus NTSC/PAL decoder

• Worldwide FM radio reception

• 250 mW power consumption

• Zero-IF down conversion architecture

• SureTrak™ digital signal processing

• Minimal external passive components

• 48-800 MHz RF reception

• 100 dB dynamic range

• <6 dB noise figure

• Fully integrated digital AGC loop

• Fully integrated channel selectivity

• 35 dBc first-adjacent rejection

• Internal blank-level clamping

• Dynamic ghosting/fading compensation

• Clocked from a single 27 MHz crystal

• All-digital video timing generation

• CCIR/ITU-601 compliant

8-bit parallel video output

• Analog and I2S digital audio output

• I2C-compliant two-wire control port

• 2.8V RF supply, 1.2V digital supply

• 68-pin MLF/QFN package

Applications

• Cellular phone television reception

• Personal video players

• Car-mounted televisions

• Adapter/PCMCIA multimedia tuners

• Personal digital assistants

• Laptop computers

TLG1100-DS v1.5

Copyright© 2006 Telegent Systems

Page 1

Confidential and Proprietary

Telegent Systems is a Trademark of Telegent Systems Inc.

Other products or brand names mentioned herein are trademarks of their respective holders

1 page

Functional Description

RF Down Conversion Block

The RF down conversion block comprises a highly linear, high dynamic range LNA coupled with a true

zero-IF mixer plus baseband signal processing. Internally, the LNA and mixer have an overall gain range

in excess of 60 dB, giving the TLG1100 excellent performance under mobile conditions. The mixer plus

baseband signal processing are implemented using a proprietary architecture, which eliminates the need

for any external SAW filters while maintaining dynamic range within the receiver. At baseband, an anti-

aliasing filter is combined with a second 60 dB variable-gain amplifier to provide the first level of adjacent-

channel rejection, as well as provide signal conditioning for interfacing into the analog-to-digital

converters. A pair of on-chip, high-performance analog-to-digital converters bridge the RF down

conversion block with the digital signal processing for the demodulator and decode functions.

NTSC/PAL Demodulator and Decoder

The Demodulator receives the digitized I/Q signals from the Analog-to-Digital converters. Digital offset

and gain control blocks condition the signals for the rest of the signal processing. Channel-select filtering

in the digital domain is applied to further reduce nearby adjacent channel interferers and improve signal

isolation. The data is then separated into 3 streams of Luma, Chroma, and Audio. The Audio stream is

FM-demodulated according to the register-selected audio standard. The Luma and Chroma data streams

are decoded to form 601-compliant fields, with framing information derived in a Sync Detection block.

The Sync Detection block extracts VSync and HSync timing information from the demodulated data

stream in a robust fashion, and is able to indicate when signal quality is low. This quality information can

be used to control a frame-hold buffer to maintain an image through momentary dropouts, thereby

improving the perceived quality of the video output. The following video signal standards are supported in

the Demodulator/Decoder block: NTSC-M, PAL-D, K, B, G, H, and I. Specific audio support is

documented further below.

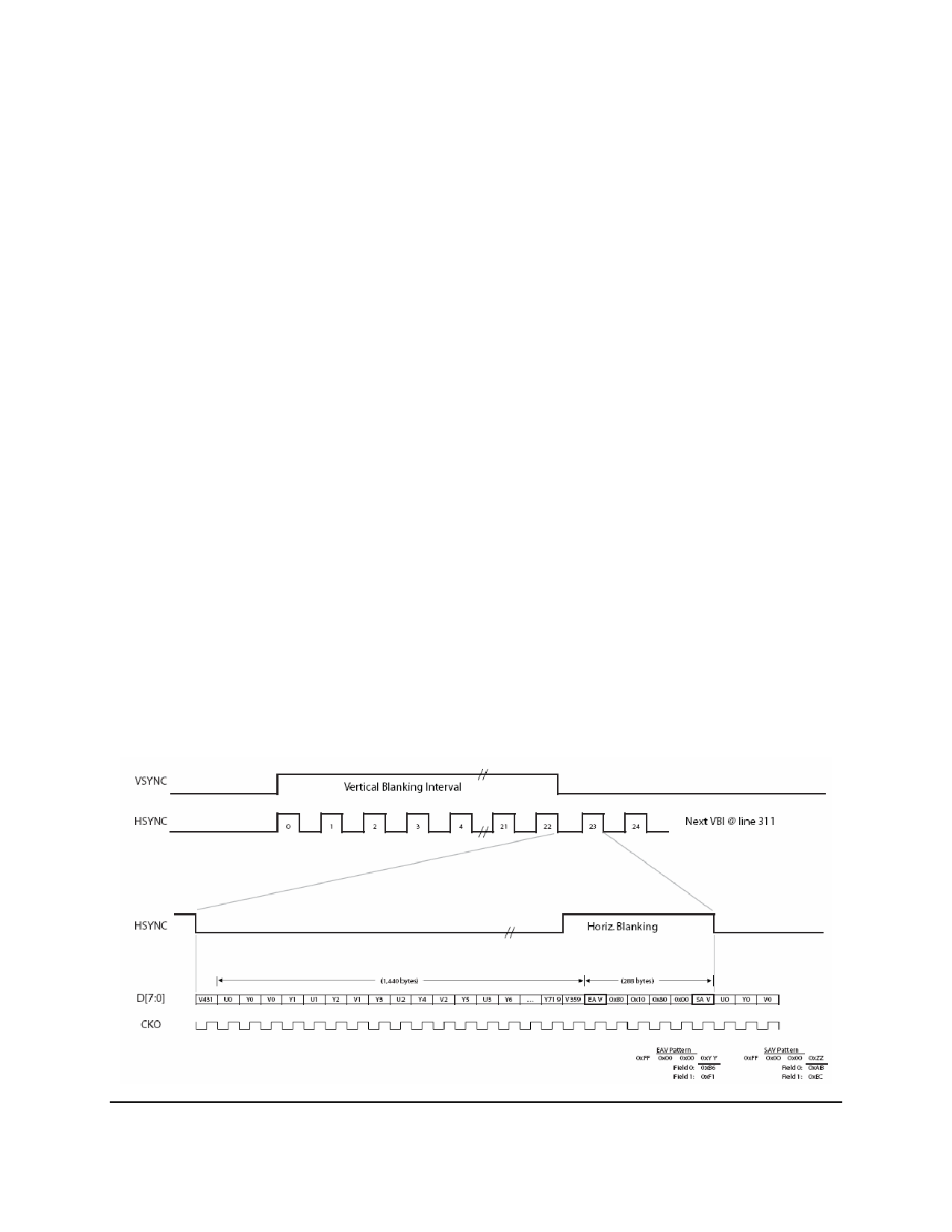

ITU-601 Interface

The digital video output port consists of an ITU-601 compliant 8-bit 4:2:2 (YCbCr) parallel interface.

Additional hardware hsync and vsync lines are provided for maximum flexibility in interfacing with existing

designs. The timing for the bus is as follows:

625 Timing

TLG1100-DS v1.5

Copyright© 2006 Telegent Systems

Page 5

Confidential and Proprietary

Telegent Systems is a Trademark of Telegent Systems Inc.

Other products or brand names mentioned herein are trademarks of their respective holders

5 Page

3 VDD_A

4 VHFP1

5 VHFN1

6 VHFP2

7 VHFN2

8 UHFP

9 UHFN

10 VDD_A

11 VDD_A

12 GND_A

13 KVCO_IN

14 LF_RET

15 VCO_REG_BYP

16 VDD_A

17 CP_OUT

18 XTALP

19 XTALN

20 SYNTH_REG_BYP

21 VDD_A

22 GND_A

23 BG_RES

24 BG_RESRET

25 VDD_A

26 GPIO_0

27 SCL

28 SDA

29 VDD_D

30 GPIO_1

31 ASD

32 ASCK

33 AMCK

34 ALRCK

35 GPIO_2

36 GPIO_3

37 VIO_D

38 D7

39 D6

40 D5

41 D4

42 VDD_D

43 D3

44 D2

45 D1

46 D0

47 GPIO_4

48 VIO_D

PWR

I

I

I

I

I

I

PWR

PWR

PWR

I

I

I

PWR

O

I/O

I/O

I

PWR

PWR

O

I

PWR

I/O

I

I/O

PWR

I/O

I/O

I/O

I/O

O

I/O

I/O

PWR

O

O

O

O

PWR

O

O

O

O

I/O

PWR

2.8V analog VDD

VHF1 LNA RF input

VHF1 LNA RF input

VHF2 LNA RF input

VHF2 LNA RF input

UHF LNA RF input

UHF LNA RF input

2.8V analog VDD

2.8V analog VDD

Analog ground

KVCO_IN - connected to loop filter output

Return reference for loop filter. DO NOT

CONNECT THIS PIN TO GROUND.

Internal regulator bypass pin

2.8V analog VDD

Charge pump output - hook to external loop filter.

27 MHz Crystal - terminal

27 MHz Crystal + terminal

Internal regulator bypass pin

2.8V analog VDD

Analog ground

Output for external reference resistor (12k);

Connect 12k resistor to BG_RESRET

Return for off-chip reference resistor. DO NOT

CONNECT THIS PIN TO GROUND.

2.8V analog VDD

GPIO 0

I2C clock

I2C data

1.2V core VDD for DSP

GPIO 1

I2S data

Audio slave clock/left sigma delta DAC

Audio master clock/right sigma delta DAC

Left/right audio sample indicator

GPIO 2

GPIO 3

2.8V VDD for digital I/O's

ITU/CCIR 601 data (MSB)

ITU/CCIR 601 data

ITU/CCIR 601 data

ITU/CCIR 601 data

1.2V core VDD for DSP

ITU/CCIR 601 data

ITU/CCIR 601 data

ITU/CCIR 601 data

ITU/CCIR 601 data (LSB)

GPIO 4

2.8V VDD for digital I/O's

TLG1100-DS v1.5

Copyright© 2006 Telegent Systems

Page 11

Confidential and Proprietary

Telegent Systems is a Trademark of Telegent Systems Inc.

Other products or brand names mentioned herein are trademarks of their respective holders

11 Page | ||

| Páginas | Total 15 Páginas | |

| PDF Descargar | [ Datasheet TLG1100.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| TLG1100 | Ultra-Low Power NTSC/PAL TV-On-Chip | Telegent Systems |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |