|

|

PDF RDA5810 Data sheet ( Hoja de datos )

| Número de pieza | RDA5810 | |

| Descripción | Direct Down-Conversion Satellite Receiver | |

| Fabricantes | RDA | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de RDA5810 (archivo pdf) en la parte inferior de esta página. Total 5 Páginas | ||

|

No Preview Available !

RDA Microelectronics, Inc. RDA5810-Fully Integrated Satellite receiver for DVB-S & DVB-S2

DATA SHEET

RDA5810

Fully Integrated, Direct Down-Conversion

Satellite Receiver for DVB-S & DVB-S2

______

The information contained herein is the exclusive property of RDA and shall not be distributed, reproduced, or disclosed in whole

or in part without prior written permission of RDA.

1 page

RDA Microelectronics, Inc. RDA5810-Fully Integrated Satellite receiver for DVB-S & DVB-S2

Reference Oscillator

The oscillator is on-chip integrated and both the crystal and crystal oscillator are supported. The 27MHz is

recommended. The centre oscillation frequency can be adjusted accurately with the XAFC pin (optional

function).

VCO

The receiver integrates four vcos which ensure covering the full receiving frequency from 900MHz to 2250MHz.

The four VCOs can be switched between each other with relevant register and the vco’s band is programmed

using 2-wire (I2C) interface. The first VCO oscillates from 1800MHz to 2700MHz, the second oscillates from

2600MHz to 3300MHz, the third oscillates from 3200MHz to 3800MHz and the final oscillates from 3700MHz to

4500MHz. After divided by two, lo signal from 900MHz to 2250MHz can be obtained. The four VCO’s oscillation

frequency overlaps at least 100MHz (i.e. lo signal overlaps 50MHz) ensures smooth transition between them and

not impacted by the LNB drift.

PLL

The fractional-N frequency synthesizer use 27MHz reference as defaut. The divders, loop filters,

phase&frequency detector, charge pump are all integrated on chip.

Baseband Output Amplifier

Class-AB architecture is selected for the output buffer, this makes it more flexible to the next Baseband solution’s

input load. The gain of this stage can also be programmed with interface to farther increase the receiver

dynamic.

I2C interface

The interface is the control unit of all the analog blocks, it is provided for configuration and monitoring all internal

registers, the I2C bus consists of two wires: serial clock line (SCL) and serial data line (SDA). The LNA’s gain,

AGC, baseband LPF’s bandwidth, VCO’s and crystal oscillator’s current, VCO’s oscillation frequency are all

controlled by the 2-wire interface.

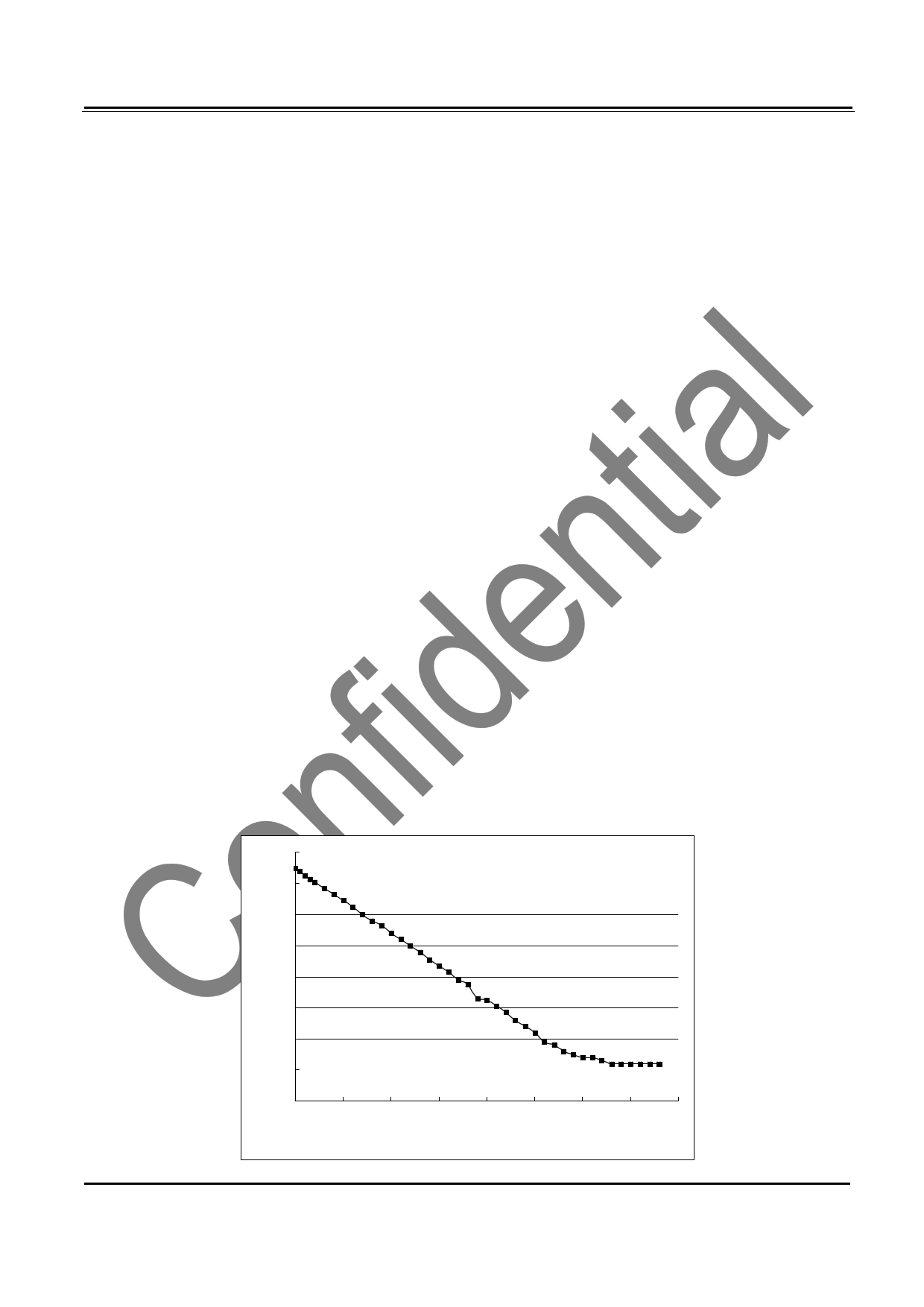

Direct AGC control

Through the AGC pin input, the receiver chain’s gain can be directly controlled by the baseband solutions. The

receiver gain changed inversely with the AGC control signal, this means that when AGC signal goes high, the

receiver gain will drop to relevant level and vice versa.

80

70

60

50

40

30

20

10

0

0 0.5 1 1.5 2 2.5 3 3.5 4

agc voltage (V)

The information contained herein is the exclusive property of RDA and shall not be distributed, reproduced, or disclosed in whole

or in part without prior written permission of RDA.

3

5 Page | ||

| Páginas | Total 5 Páginas | |

| PDF Descargar | [ Datasheet RDA5810.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| RDA5810 | Direct Down-Conversion Satellite Receiver | RDA |

| RDA5812 | Direct Down-Conversion Satellite Receiver | RDA |

| RDA5815 | Fully Integrated Satellite receiver | RDA |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |