|

|

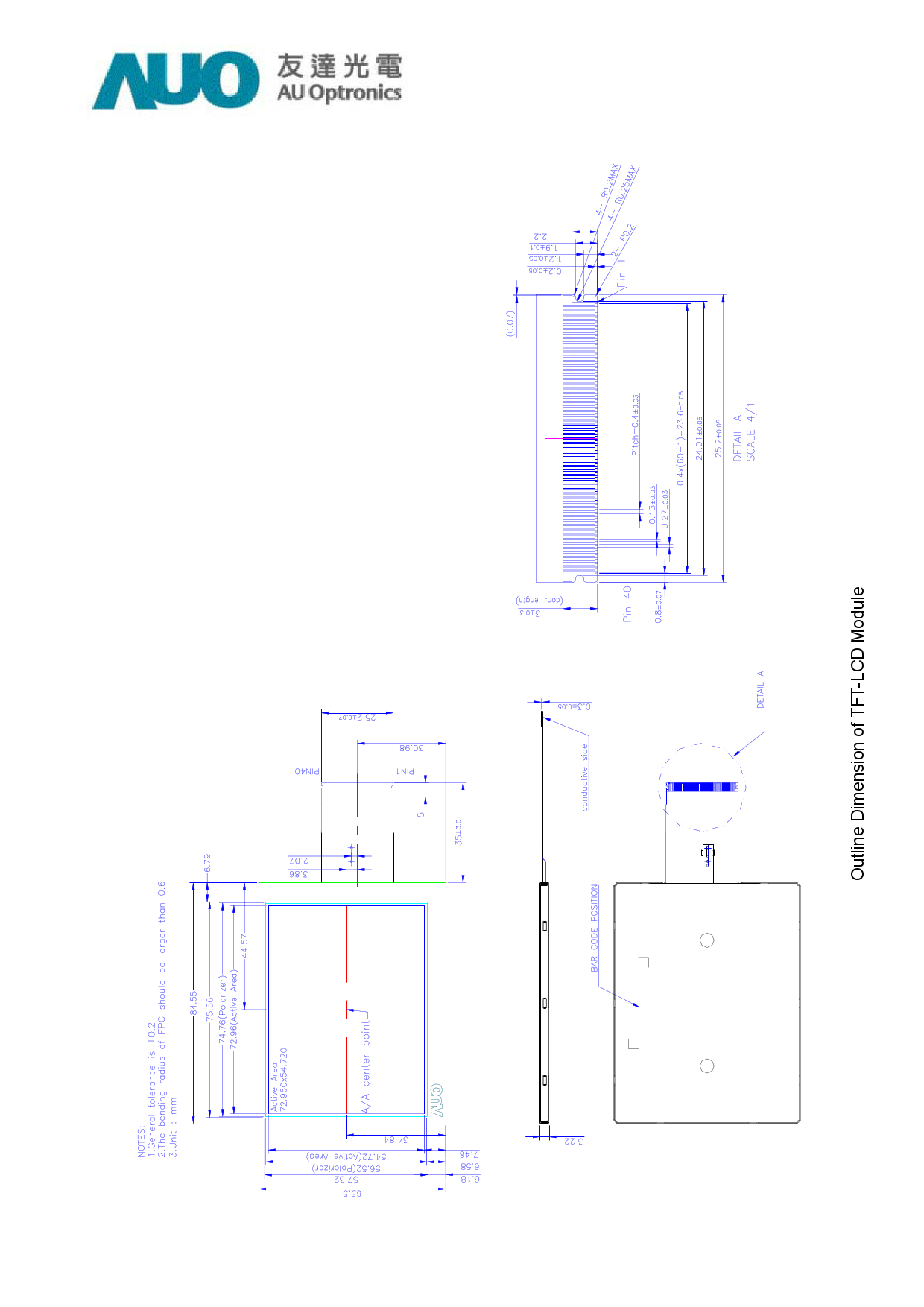

PDF A036QN02-V1 Data sheet ( Hoja de datos )

| Número de pieza | A036QN02-V1 | |

| Descripción | COLOR TFT-LCD MODULE | |

| Fabricantes | AUO | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de A036QN02-V1 (archivo pdf) en la parte inferior de esta página. Total 30 Páginas | ||

|

No Preview Available !

Version Revise Date

0 22/Jul/2005

0.1 16/Aug/2005

0.2 8/Sep/2005

0.3 03/Nov/2005

0

Page

Record of Revision

Content

First draft.

18 Add “(b) In Parallel Data Interface” figure.

3

6-8

9-14

18

19

22

24

3

4

11

16-17

18-20

21

A036QN02 V1 only support CCIR-656, serial 8bit. RGB,

and TTL 8bit

Correct I/O description

Modify register setting and description

Delete Note 2 of 3.5.1

Delete “The fist line is at 14th that will be display on panel” of

note.

Add item “Vsync to 1st active line” of 3.5.2.1

Add 3-wire serial communication AC timing figure.

Add A036QN02 V0 support “CCIR-601, YUV” interface

Change panel surface treatment to “Hard Coating 3H” after

Dec/ ’05.

Add register setting of “parallel RGB data input”.

Update application circuit

Correct symbol. Delete “The fist line is at 14th that will be

display on panel.”

Correct third-item from “Hsync pulse width” to “Hsync

Period”

Add timing parameter “Hsync pluse width”, “Vsync period”,

“Vertical active area”, “Vsync pulse width” at 3.5.2.1.

Data Modul AG - www.data-modul.com

1

1 page

Data Modul AG - www.data-modul.com

0

5

5 Page

4

NTSC/PAL selection.

“0” ÎNTSC input format.(default)

“1” ÎPAL input format.

“0XX0” ÎUPS051.(default)

“0XX1” ÎParallel RGB data input.

“1000” ÎUPS052 320RGB 24.54MHz.

“1001” ÎUPS052 360RGB 27MHz.

3~0

Input data format.

“1010” ÎYUV mode A 24.54MHz.

“1011” ÎYUV mode A 27MHz.

“1100” ÎYUV mode B 24.54MHz.

“1101” ÎYUV mode B 27MHz.

“1110” ÎCCIR656 24.54MHz.

“1111” ÎCCIR656 27MHHz.

Note: Bold blue sentence is suggested setting for A036QN02 V1. Customer needs to

manually set bit 10~6.

Register R2

Bit Function

7~0

Horizontal data

Start delay selection

“00000000” ÎThs=Thstyp-128 CL period.

“10000000” ÎThs=Thstyp.(default)

“11111111” ÎThs=Thstyp+127 CL period.

Note 1: Bold blue sentence is suggested setting for A036QN02 V1.

Note 2: Ths: Horizontal data start pulse.

Thstyp: Typical values of horizontal data start pulse.

Register R3

Bit Function

10

Gate driver

Vgoff setting

“0” ÎVgoff=Vgoff_L. (default)

“1” Î Vgoff switches between Vgoff_L and

Vgoff_H.

9

Dopt function

“0” ÎR,G,B are sample simultaneous.(default)

“1” ÎR,G,B are sample sequentially.

8~5

start

Source driver

pulse delay selection.

“0000” ÎHorizontal start display=Ths.(default)

“1111”ÎHorizontal start display=Ths+15 CL period

(default)

4~0

Gate driver start pulse

delay selection

“00000” ÎTstv=Tstvtyp-16 Hsync period

“10000” ÎTstv=Tstvtyp.(default)

“11111” Î Tstv=Tstvtyp+15 Hsync period

Note: Bold blue sentence is suggested setting for A036QN02 V1. Customer needs to

manually set bit 10.

Data Modul AG - www.data-modul.com

11

11 Page | ||

| Páginas | Total 30 Páginas | |

| PDF Descargar | [ Datasheet A036QN02-V1.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| A036QN02-V0 | COLOR TFT-LCD MODULE | AUO |

| A036QN02-V1 | COLOR TFT-LCD MODULE | AUO |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |