|

|

PDF P6103ASU8 Data sheet ( Hoja de datos )

| Número de pieza | P6103ASU8 | |

| Descripción | 5V/12V Synchronous-Rectified Buck Controller | |

| Fabricantes | uPI Semiconductor | |

| Logotipo | ||

Hay una vista previa y un enlace de descarga de P6103ASU8 (archivo pdf) en la parte inferior de esta página. Total 15 Páginas | ||

|

No Preview Available !

uP6103

5V/12V Synchronous-Rectified

Buck Controller with Reference Input

General Description

Features

The uP6103 is a compact synchronous-rectified buck

controller specifically designed to operate from 5V or 12V

supply voltage and to deliver high quality output voltage as

low as 0.4V. These SOP-8 and PSOP-8 devices operate at

fixed 200/300 kHz frequency and provide an optimal level

of integration to reduce size and cost of the power supply.

The uP6103 supports both tracking mode and stand-alone

mode operation. The output voltage is tightly regulated to

the external reference voltage from 0.4V to 3.0V at tracking

mode or to internal 0.6V reference at stand-alone mode.

This controller integrates internal MOSFET drivers that

support 12V+12V bootstrapped voltage for high efficiency

power conversion. The bootstrap diode is built-in to simplify

the circuit design and minimize external part count.

Other features include internal softstart, undervoltage

protection, overcurrent protection and shutdown function.

With aforementioned functions, this part provides

customers a compact, high efficiency, well-protected and

cost-effective solutions. This part is available in SOP-8 and

PSOP-8 packages.

Ordering Information

Order Number Package Top Marking

Remark

uP6103S8 SOP-8L uP6103S8

200kHz

uP6103AS8 SOP-8L uP6103AS8

300kHz

uP6103ASU8 PSOP-8L uP6103ASU8

300kHz

Note: uPI products are compatible with the current IPC/

JEDEC J-STD-020 requirements. They are halogen-free,

RoHS compliant and 100% matte tin (Sn) plating that are

suitable for use in SnPb or Pb-free soldering processes.

Operate from 5V or 12V Supply Voltage

3.3V to 12V VIN Input Range

0.6 VREF with 1.5% Accuracy

Output Range from VREF to 80% of VIN

Support Tracking Mode and Stand Alone Mode

Operation

Simple Single-Loop Control Design

Voltage-Mode PWM Control

Fast Transient Response

High-Bandwidth Error Amplifier

0% to 80% Duty Cycle

Lossless, Programmable Overcurrent Protection

Uses Lower MOSFET RDS(ON)

200/300 kHz Fixed Frequency Oscillator

Internal Soft Start

Integrated Bootstrap Diode

RoHS Compliant and Halogen Free

Applications

Power Supplies for Microprocessors or

Subsystem Power Supplies

Cable Modems, Set Top Boxes, and xDSL

Modems

Industrial Power Supplies; General Purpose

Supplies

5V or 12V Input DC-DC Regulators

Low Voltage Distributed Power Supplies

Pin Configuration & Typical Application Circuit

BOOT

UGATE

GND

LGATE

18

27

36

45

SOP-8

PHASE

REFIN

FB

VCC

BOOT

UGATE

GND

LGATE

18

27

GND

36

45

PSOP-8

PHASE

REFIN

FB

VCC

Reference

Input

Disable

Enable

REFIN

7

VCC

5

BOOT

1

UGATE

2

8 PHASE

FB

6

Option

4 LGATE

3

GND

uPI Semiconductor Corp., http://www.upi-semi.com

Rev. F00, File Name: uP6103-DS-F0000

VIN

VOUT

1

1 page

uP6103

Functional Description

to 5VDD in 66ms after the softstart cycle is intiated (for

uP6103). The ramp is created digitally, so there will be 100

small discrete steps. Accordingly, the output voltage will

follow the SS signal and ramp up smoothly to its target

level.

The SS signal keeps ramping up after it execeeds the

internal reference VREF. However, the reference voltage VREF

takes over the behavior of error amplifier after SS > VREF.

When the SS signal climb to its ceiling voltage (5V), the

uP6103 claims the end of softstart cyclce and enable the

under voltage protection of the output voltage.

For internal reference voltage, the effective ramp-up time of

the output voltage is about 3.6ms. For external reference

voltage, the effective ramp up time output voltage is

calculated as:

uP6103, 300kHz for uP6103A. Higher switching frequncy

allows higher control bandwidth and faster transient

response. However higher swithcing frequency results in

higher power loss in both controller and power MOSFETs.

The uP6103 detects PHASE voltage for the existence of

power input when the UGATE turns on the first time. If the

PHASE voltage does not exceed 3.0V when the UGATE

turns on, the uP6103 asserts that power input in not ready

and stops the softstart cycle. However, the internal SS

continues ramping up to 3.3VDD. Another softstart is

initiated after SS ramps up to 3.3VDD. The hiccup period

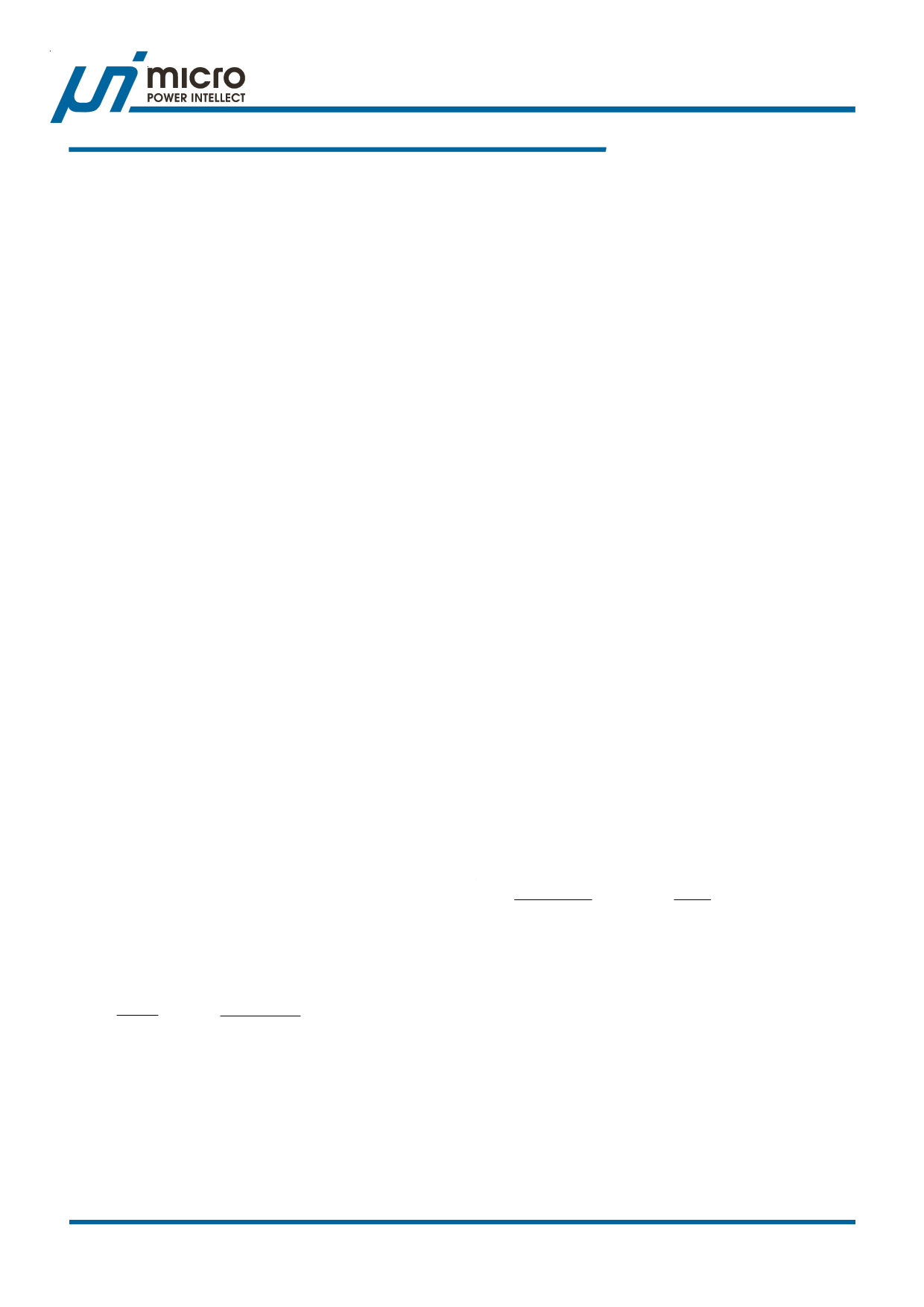

is about 6.4ms. Figure 3 shows the start up interval where

VIN does not present initially.

TSS = 6 × VREF

(ms)

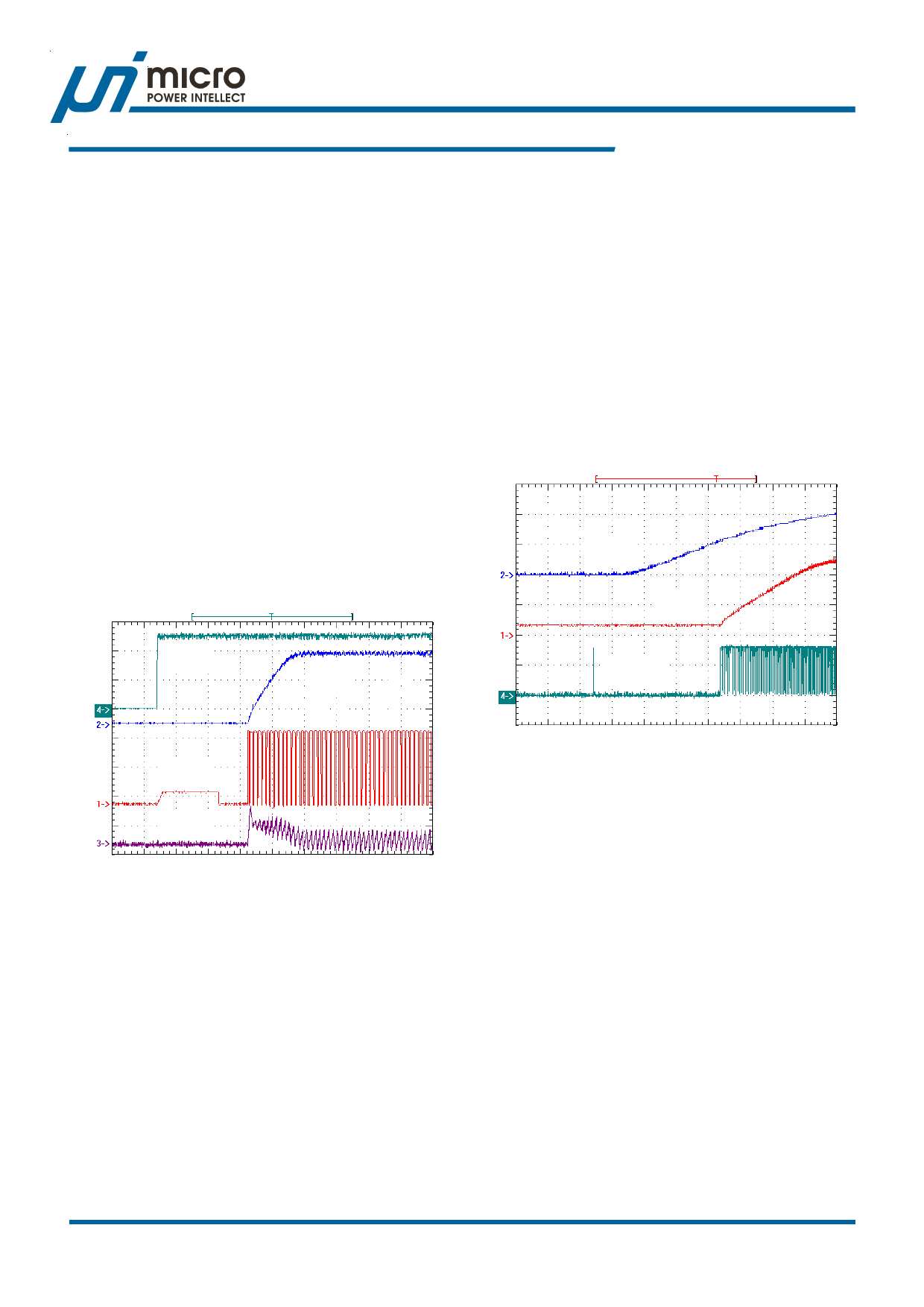

Figure 2 shows a typical start up interval where the REFIN

pin has been released from a grounded (system shutdown)

state.

VIN

5V/Div

VOUT

5V/Div

VIN

5V/Div

VOUT

0 .5 V /D iv

LGATE

5V/Div

1ms/Div

LGATE

5 V /D iv

IX

2.5/Div

2ms/Div

Figure 2. Softstart Behavior.

Power Input Detection

The uP6103 detects PHASE voltage for the present of power

input when the UGATE turns on the first time. If the PHASE

voltage does not exceed 3.0V when the UGATE turns on,

the uP6103 asserts that power input in not ready and stops

the softstart cycle. However, the internal SS continues

ramping up to 5VDD. Another softstart is initiated after SS

ramps up to 5VDD. The hiccup period is about 12ms. Figure

3 shows the start up interval where VIN does not present

initially.

Switching Frequency

The switching frequency is fixed and can not be changed

externally. Typical switching frequency is 200kHz for

Figure 3. Softstart where VIN does not Present Initially.

Overcurrent Protection (OCP)

The uP6103 detects voltage drop across the lower MOSFET

(VPHASE) for overcurrent protection when it is turn on. If VPHASE

is lower than VOCP = -375mV, the uP6103 asserts OCP and

shuts down the converter.

Another factor should taken into consideration is the ripple

of the inductor current. The current near the valley of the

ripple current is used for OCP, resulting the averaged OCP

level a little higher than the calculated value.

Undervoltage Protection (UVP)

The FB voltage is monitored for undervoltage protection.

The UVP threshold level is typical 0.4V for both stand-

alone and tracking mode. The uP6103 shuts down upon

the detection of UVP and can be reset only by POR or

toggling REFIN pin.

uPI Semiconductor Corp., http://www.upi-semi.com

Rev. F00, File Name: uP6103-DS-F0000

5

5 Page

uP6103

Application Information

Power MOSFET Selection

External component selection is primarily determined by

the maximum load current and begins with the selection of

power MOSFET switches. The uP6103 requires two

external N-channel power MOSFETs for upper (controlled)

and lower (synchronous) switches. Important parameters

for the power MOSFETs are the breakdown voltage V(BR)DSS,

on-resistance RDS(ON), reverse transfer capacitance CRSS,

maximum current IDS(MAX), gate supply requirements, and

thermal management requirements.

The gate drive voltage is powered by VCC pin that receives

4.5V~13.2V supply voltage. When operating with a 12V

power supply for VCC (or down to a minimum supply

voltage of 8V), a wide variety of NMOSFETs can be used.

Logic-level threshold MOSFET should be used if the input

voltage is expected to drop below 8V. Since the lower

MOSFET is used as the current sensing element, particular

attention must be paid to its on-resistance. Look for RDS(ON)

ratings at lowest gate driving voltage.

Special cautions should be exercised on the lower switch

exhibiting very low threshold voltage VGS(TH). The shoot-

through protection present aboard the uP6103 may be

circumvented by these MOSFETs if they have large

parasitic impedences and/or capacitances that would inhibit

the gate of the MOSFET from being discharged below its

threshold level before the complementary MOSFET is

turned on. Also avoid MOSFETs with excessive switching

times; the circuitry is expecting transitions to occur in under

50 nsec or so.

In high-current applications, the MOSFET power

dissipation, package selection and heatsink are the

dominant design factors. The power dissipation includes

two loss components; conduction loss and switching loss.

The conduction losses are the largest component of power

dissipation for both the upper and the lower MOSFETs.

These losses are distributed between the two MOSFETs

according to duty cycle. Since the uP6103 is operating in

continuous conduction mode, the duty cycles for the

MOSFETs are:

DUP

=

VOUT

VIN

;

DLO

=

VIN

− VOUT

VIN

The resulting power dissipation in the MOSFETs at

maximum output current are:

PUP = IO2 UT × RDS(ON) × DUP + 0.5 × IOUT × VIN × TSW × fOSC

PLO = IO2 UT × RDS(ON) × DLO

where TSW is the combined switch ON and OFF time.

Both MOSFETs have I2R losses and the top MOSFET

includes an additional term for switching losses, which are

largest at high input voltages. The bottom MOSFET losses

are greatest when the bottom duty cycle is near 100%,

during a short-circuit or at high input voltage. These

equations assume linear voltage current transitions and do

not adequately model power loss due the reverse-recovery

of the lower MOSFET’s body diode. Ensure that both

MOSFETs are within their maximum junction temperature

at high ambient temperature by calculating the temperature

rise according to package thermal-resistance

specifications. A separate heatsink may be necessary

depending upon MOSFET power, package type, ambient

temperature and air flow.

The gate-charge losses are dissipated by the uP6103 and

don’t heat the MOSFETs. However, large gate charge

increases the switching interval, TSW that increases the

MOSFET switching losses. The gate-charge losses are

calculated as:

PG = VCC × (VCC × (CISS _ UP + CISS _ LO ) + VIN × CRSS ) × fOSC

where CISS_UP is the input capacitance of the upper

MOSFET, CISS_LO is the input capacitance of the lower

MOSFET, and CRSS_UP is the reverse transfer capacitance

of the upper MOSFET. Make sure that the gate-charge loss

will not cause over temperature at uP6103, especially with

large gate capacitance and high supply voltage.

Output Inductor Selection

Output inductor selection usually is based the

considerations of inductance, rated current, size

requirement, and DC resistance (DC)

Given the desired input and output voltages, the inductor

value and operating frequency determine the ripple current:

∆IL

=

1

fOSC × LOUT

× VOUT

× (1−

VOUT

VIN

)

Lower ripple current reduces core losses in the inductor,

ESR losses in the output capacitors and output voltage

ripple. Highest efficiency operation is obtained at low

frequency with small ripple current. However, achieving this

requires a large inductor. There is a tradeoff between

component size, efficiency and operating frequency. A

reasonable starting point is to choose a ripple current that

is about 40% of IOUT(MAX).

There is another tradeoff between output ripple current/

voltage and response time to a transient load. Increasing

the value of inductance reduces the output ripple current

and voltage. However, the large inductance values reduce

the converter’s response time to a load transient.

uPI Semiconductor Corp., http://www.upi-semi.com

Rev. F00, File Name: uP6103-DS-F0000

11

11 Page | ||

| Páginas | Total 15 Páginas | |

| PDF Descargar | [ Datasheet P6103ASU8.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| P6103ASU8 | 5V/12V Synchronous-Rectified Buck Controller | uPI Semiconductor |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |