|

|

PDF TC58TEG5DCJ Data sheet ( Hoja de datos )

| Número de pieza | TC58TEG5DCJ | |

| Descripción | NAND memory Toggle DDR1.0 | |

| Fabricantes | Toshiba | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de TC58TEG5DCJ (archivo pdf) en la parte inferior de esta página. Total 30 Páginas | ||

|

No Preview Available !

TOSHIBA CONFIDENTIAL TC58TEG5DCJTAx0

TOSHIBA

NAND memory

Toggle DDR1.0

Technical Data Sheet

Rev. 0.2

2012 – 03 – 01

TOSHIBA

Semiconductor & Storage Products

Memory Division

0 TENTATIVE 2012-03-01C

1 page

TOSHIBA CONFIDENTIAL TC58TEG5DCJTAx0

LIST of TABLES

Table 1 Pin Descriptions ............................................................................................................................................ 9

Table 3 Absolute Maximum Rating .......................................................................................................................... 12

Table 4 Operating Temperature Condition ............................................................................................................... 13

Table 5 Recommended Operating Condition........................................................................................................... 13

Table 6 Valid Blocks................................................................................................................................................. 13

Table 7 AC Overshoot/Undershoot Specification ..................................................................................................... 14

Table 8 DC & Operating Characteristics for Toggle VccQ=3.3V .............................................................................. 15

Table 9 DC & Operating Characteristics for Toggle VccQ=1.8V .............................................................................. 16

Table 10 DC & Operating Characteristics for SDR VccQ=1.8V and 3.3V .............................................................. 17

Table 11 Input/ Output capacitance ......................................................................................................................... 17

Table 12 DQ Drive Strength Settings ....................................................................................................................... 17

Table 13 Testing Conditions for Impedance Values ................................................................................................. 17

Table 14 Output Drive Strength Impedance Values ................................................................................................. 18

Table 15 Pull-up and Pull-down Output Impedance Mismatch ................................................................................ 18

Table 16 Derating factor .......................................................................................................................................... 19

Table 17 Input Slew Rate......................................................................................................................................... 19

Table 18 Testing Conditions for Input Slew Rate ..................................................................................................... 19

Table 19 Output Slew Rate Requirements............................................................................................................... 19

Table 20 Testing Conditions for Output Slew Rate .................................................................................................. 20

Table 21 The addressing of this device. .................................................................................................................. 23

Table 23 Toggle DDR1.0 Interface Mode Selection ................................................................................................. 29

Table 24 SDR Interface Mode Selection.................................................................................................................. 29

Table 25 Timing Parameters Description ................................................................................................................. 44

Table 26 AC Timing Charateristics........................................................................................................................... 46

Table 27 AC Test Conditions.................................................................................................................................... 48

Table 28 Read/Program/Erase Timing Characteristics ............................................................................................ 48

Table 29 Basic Command Sets................................................................................................................................ 49

Table 30 Set feature addresses ............................................................................................................................... 55

Table 31 Driver Strength Setting Data ..................................................................................................................... 56

Table 32 Interface change Setting Data................................................................................................................... 56

Table 33 00h Address ID Definition Table ................................................................................................................ 57

Table 35 3rd ID Data................................................................................................................................................ 57

Table 36 4th ID Data................................................................................................................................................ 57

Table 38 6th ID Data................................................................................................................................................ 58

Table 39 40h Address ID Cycle ............................................................................................................................... 58

Table 40 40h Address ID Definition ......................................................................................................................... 58

Table 41 Read Status Definition for 70h .................................................................................................................. 59

Table 42 Read Status Definition for 71h .................................................................................................................. 59

Table 43 Extended Command Sets......................................................................................................................... 62

Table 44 Parameter Page Definitions...................................................................................................................... 65

Table 45 Read Status Enhanced Definition ............................................................................................................. 70

Table 46 Read LUN#0 Status Definition .................................................................................................................. 71

4 TENTATIVE 2012-03-01C

5 Page

TOSHIBA CONFIDENTIAL TC58TEG5DCJTAx0

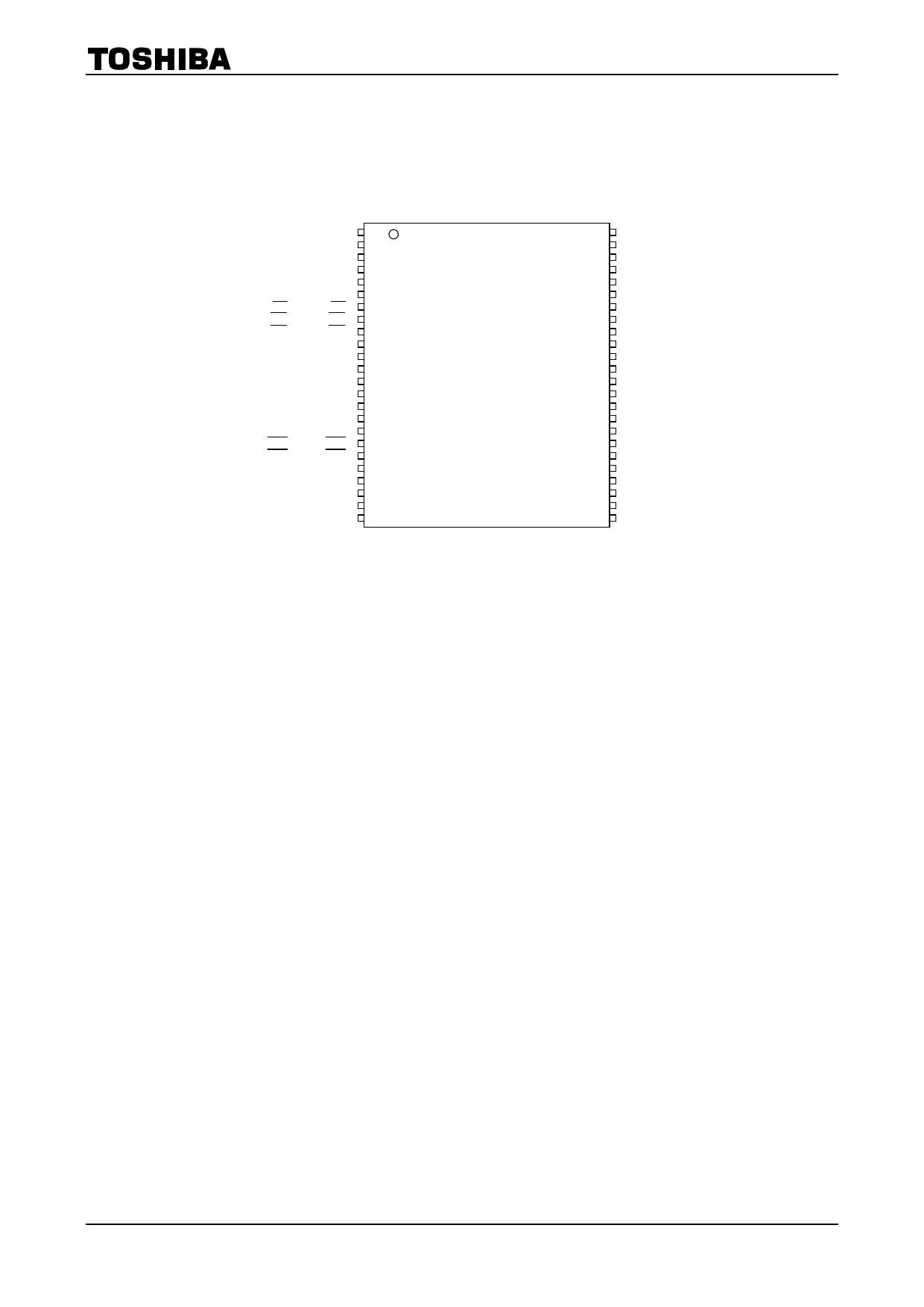

2.2. PIN ASSIGNMENT (TOP VIEW)

SDR

only

Vcc

Vss

NC

NC

NC

NC

RY / BY

RE

CE

NC

NC

VCC

VNSCS

NC

CLE

ALE

WE

WP

NC

NC

NC

Vss

Vcc

SDR/Toggle

DDR1.0

Vcc

Vss

NC

NC

NC

NC

RY / BY

RE

CE

NC

NC

VCC

VNSCS

NC

CLE

ALE

WE

WP

NC

NC

NC

Vss

Vcc

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

Tx58TEG5DCJ

SDR/Toggle SDR

DDR1.0 only

48 Vss

Vss

47 NC

NC

46 VssQ NU or VssQ

45 VccQ NU or VccQ

44 DQ7

DQ7

43 DQ6

DQ6

42 DQ5

DQ5

41 DQ4

DQ4

40 VssQ NU or VssQ

39 VccQ NU or VccQ

38 VccQ VccQ

37 VCC

36

35

VDSQSS

VCC

NVSUS

34 VccQ VccQ

33 VssQ NU or VssQ

32 DQ3

DQ3

31 DQ2

DQ2

30 DQ1

DQ1

29 DQ0

DQ0

28 VccQ NU or VccQ

27 VssQ NU or VssQ

26 NC

NC

25 Vss

Vss

10 TENTATIVE 2012-03-01C

11 Page | ||

| Páginas | Total 30 Páginas | |

| PDF Descargar | [ Datasheet TC58TEG5DCJ.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| TC58TEG5DCJ | NAND memory Toggle DDR1.0 | Toshiba |

| TC58TEG5DCJTA00 | NAND memory Toggle DDR1.0 | Toshiba |

| TC58TEG5DCJTAI0 | NAND memory Toggle DDR1.0 | Toshiba |

| TC58TEG5DCJTAx0 | NAND memory Toggle DDR1.0 | Toshiba |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |