|

|

PDF CYD02S36V18 Data sheet ( Hoja de datos )

| Número de pieza | CYD02S36V18 | |

| Descripción | Dual Port SRAM | |

| Fabricantes | Cypress Semiconductor | |

| Logotipo | ||

Hay una vista previa y un enlace de descarga de CYD02S36V18 (archivo pdf) en la parte inferior de esta página. Total 30 Páginas | ||

|

No Preview Available !

CYDXXS72V18

CYDXXS36V18

CYDXXS18V18

FullFlex™ Synchronous SDR

Dual Port SRAM

FullFlex™ Synchronous SDR Dual Port SRAM

Features

■ True dual port memory enables simultaneous access the

shared array from each port

■ Synchronous pipelined operation with single data rate (SDR)

operation on each port

❐ SDR interface at 200 MHz

❐ Up to 28.8 Gb/s bandwidth (200 MHz × 72-bit × 2 ports)

■ Selectable pipelined or flow-through mode

■ 1.5 V or 1.8 V core power supply

■ Commercial and Industrial temperature

■ IEEE 1149.1 JTAG boundary scan

■ Available in 484-ball PBGA (× 72) and 256-ball FBGA (× 36

and × 18) packages

■ FullFlex72 family

❐ 36-Mbit: 512 K × 72 (CYD36S72V18)

❐ 18-Mbit: 256 K × 72 (CYD18S72V18)

❐ 9-Mbit: 128 K × 72 (CYD09S72V18)

■ FullFlex36 family

❐ 36-Mbit: 1 M × 36 (CYD36S36V18)

❐ 18-Mbit: 512 K × 36 (CYD18S36V18)

❐ 9-Mbit: 256 K × 36 (CYD09S36V18)

❐ 2-Mbit: 64 K × 36 (CYD02S36V18)

■ FullFlex18 family

❐ 36-Mbit: 2 M × 18 (CYD36S18V18)

❐ 18-Mbit: 1 M × 18 (CYD18S18V18)

❐ 9-Mbit: 512 K × 18 (CYD09S18V18)

■ Built in deterministic access control to manage address

collisions

❐ Deterministic flag output upon collision detection

❐ Collision detection on back-to-back clock cycles

❐ First busy address readback

■ Advanced features for improved high speed data transfer and

flexibility

❐ Variable impedance matching (VIM)

❐ Echo clocks

❐ Selectable LVTTL (3.3 V), Extended HSTL (1.4 V to 1.9 V),

1.8 V LVCMOS, or 2.5 V LVCMOS IO on each port

❐ Burst counters for sequential memory access

❐ Mailbox with interrupt flags for message passing

❐ Dual chip enables for easy depth expansion

Functional Description

The FullFlex™ dual port SRAM families consist of 2-Mbit, 9-Mbit,

18-Mbit, and 36-Mbit synchronous, true dual port static RAMs

that are high speed, low power 1.8 V or 1.5 V CMOS. Two ports

are provided, enabling simultaneous access to the array.

Simultaneous access to a location triggers deterministic access

control. For FullFlex72 these ports operate independently with

72-bit bus widths and each port is independently configured for

two pipelined stages. Each port is also configured to operate in

pipelined or flow through mode.

The advanced features include the following:

■ Built in deterministic access control to manage address

collisions during simultaneous access to the same memory

location

■ Variable impedance matching (VIM) to improve data

transmission by matching the output driver impedance to the

line impedance

■ Echo clocks to improve data transfer

To reduce the static power consumption, chip enables power

down the internal circuitry. The number of latency cycles before

a change in CE0 or CE1 enables or disables the databus

matches the number of cycles of read latency selected for the

device. For a valid write or read to occur, activate both chip

enable inputs on a port.

Each port contains an optional burst counter on the input address

register. After externally loading the counter with the initial

address, the counter increments the address internally.

Additional device features include a mask register and a mirror

register to control counter increments and wrap around. The

counter interrupt (CNTINT) flags notify the host that the counter

reaches maximum count value on the next clock cycle. The host

reads the burst counter internal address, mask register address,

and busy address on the address lines. The host also loads the

counter with the address stored in the mirror register by using the

retransmit functionality. Mailbox interrupt flags are used for

message passing, and JTAG boundary scan and asynchronous

Master Reset (MRST) are also available. The Logic Block

Diagram on page 2 shows these features.

The FullFlex72 is offered in a 484-ball plastic BGA package. The

FullFlex36 and FullFlex18 are available in 256-ball fine pitch

BGA package except the 36-Mbit devices which are offered in

484-ball plastic BGA package.

Cypress Semiconductor Corporation • 198 Champion Court

Document Number: 38-06082 Rev. *O

• San Jose, CA 95134-1709 • 408-943-2600

Revised February 5, 2013

http://www.Datasheet4U.com

1 page

CYDXXS72V18

CYDXXS36V18

CYDXXS18V18

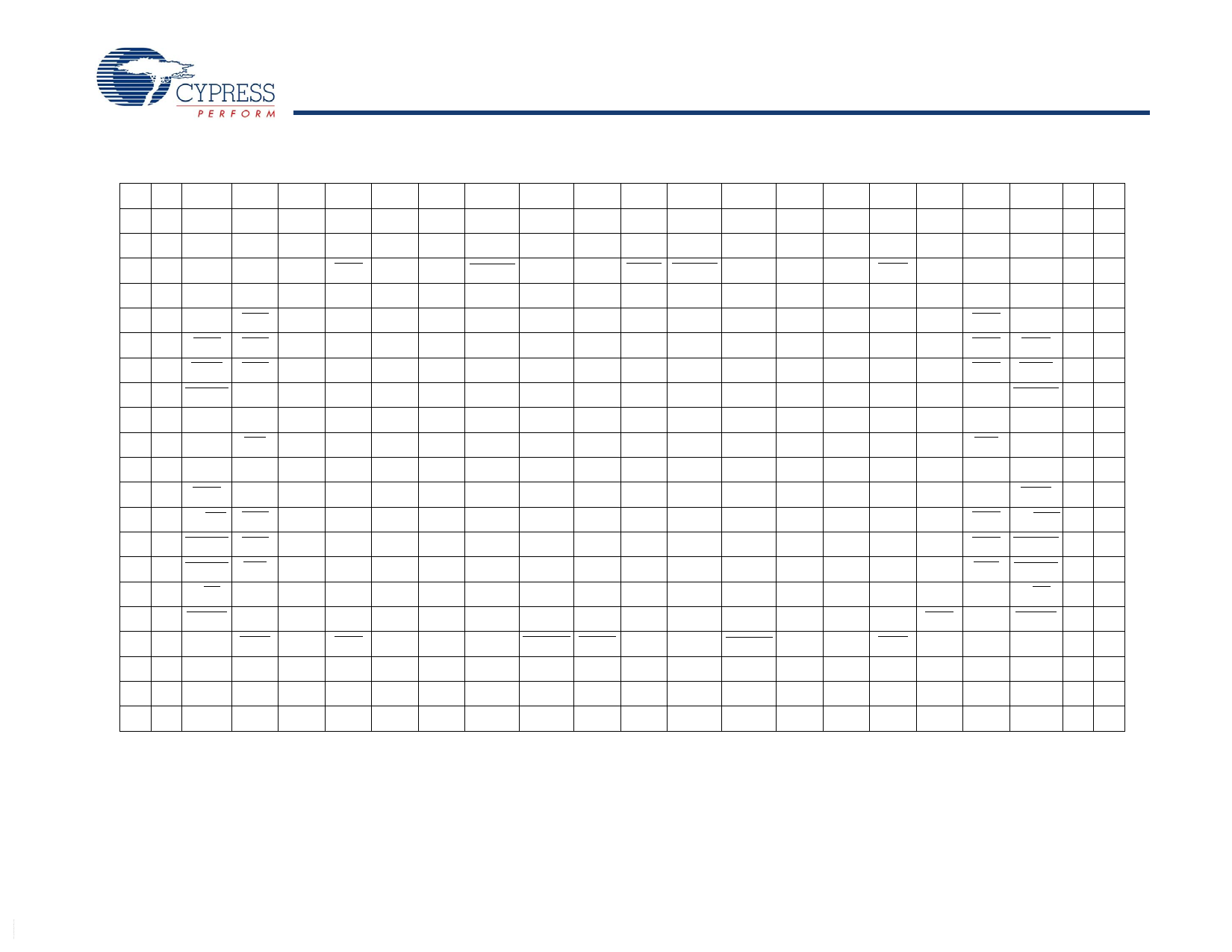

Figure 2. FullFlex36 SDR 484-ball BGA Pinout (Top View)[9]

12

3

4

5

6

7

8

9

10 11 12 13

14 15 16 17 18 19 20 21 22

A DNU DNU DNU DNU DNU DQ33L DQ30L DQ27L DQ24L DQ21L DQ18L DQ18R DQ21R DQ24R DQ27R DQ30R DQ33R DNU DNU DNU DNU DNU

B DNU DNU DNU DNU DNU DQ34L DQ31L DQ28L DQ25L DQ22L DQ19L DQ19R DQ22R DQ25R DQ28R DQ31R DQ34R DNU DNU DNU DNU DNU

C DNU DNU

D DNU DNU

VSS

VSS

VSS

VSS

DNU

VSS

DQ35L DQ32L DQ29L DQ26L DQ23L DQ20L DQ20R DQ23R DQ26R DQ29R DQ32R DQ35R

CQ1L CQ1L VSS LOWSPDL PORTSTD0L ZQ0L[10] BUSYL CNTINTL PORTSTD1L DNU CQ1R CQ1R

DNU

VSS

VSS

VSS

VSS

VSS

DNU DNU

DNU DNU

E DNU DNU VDDIOL VSS VSS VDDIOL VDDIOR VDDIOR VDDIOR VDDIOR VTTL VTTL VTTL VDDIOL VDDIOL VDDIOL VDDIOL DNU VSS VDDIOR DNU DNU

F DNU DNU CE1L CE0L VDDIOL VDDIOL VDDIOR VDDIOR VDDIOR VCORE VCORE VCORE VCORE VDDIOL VDDIOL VDDIOL VDDIOR VDDIOR CE0R CE1R DNU DNU

G A0L A1L RETL BE2L VDDIOL VDDIOL VREFL VSS

VSS

VSS

VSS VSS

VSS

VSS

VSS VREFR VDDIOR VDDIOR BE2R RETR A1R A0R

H A2L A3L WRPL BE3L VDDIOL VDDIOL VSS VSS

VSS

VSS

VSS VSS

VSS

VSS

VSS VSS VDDIOR VDDIOR BE3R WRPR A3R A2R

J A4L A5L READYL

K A6L A7L ZQ1L[10]

DNU

DNU

VDDIOL VDDIOL

VTTL VCORE

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS VDDIOR VDDIOR DNU READYR A5R A4R

VSS VCORE VDDIOR DNU ZQ1R[10] A7R A6R

L A8L A9L CL

OEL VTTL VCORE VSS VSS

VSS

VSS

VSS VSS

VSS

VSS

VSS VSS VCORE VTTL OER

CR A9R A8R

M A10L A11L VSS DNU VTTL VCORE VSS VSS

VSS

VSS

VSS VSS

VSS

VSS

VSS VSS VCORE VTTL DNU

VSS A11R A10R

N A12L A13L ADSL DNU VDDIOL VCORE VSS VSS

VSS

VSS

VSS VSS

VSS

VSS

VSS VSS VCORE VTTL DNU ADSR A13R A12R

P A14L A15L CNT/MSKL BE1L VDDIOL VDDIOL VSS VSS

VSS

VSS

VSS VSS

VSS

VSS

VSS VSS VDDIOR VDDIOR BE1R CNT/MSKR A15R A14R

R A16L A17L CNTENL BE0L VDDIOL VDDIOL VSS VSS

VSS

VSS

VSS VSS

VSS

VSS

VSS VSS VDDIOR VDDIOR BE0R CNTENR A17R A16R

T A18L A19L CNTRSTL INTL VDDIOL VDDIOL VREFL VSS

VSS

VSS

VSS VSS

VSS

VSS

VSS VREFR VDDIOR VDDIOR INTR CNTRSTR A19R A18R

U DNU DNU R/WL CQENL VDDIOL VDDIOL VDDIOR VDDIOR VDDIOR VCORE VCORE VCORE VCORE VDDIOL VDDIOL VDDIOL VDDIOR VDDIOR CQENR R/WR DNU DNU

V DNU DNU FTSELL VDDIOL DNU VDDIOR VDDIOR VDDIOR VDDIOR VTTL VTTL VTTL VDDIOL VDDIOL VDDIOL VDDIOL VDDIOR TRST VDDIOR FTSELR DNU DNU

W DNU DNU VSS MRST VSS CQ0L CQ0L DNU PORTSTD1R CNTINTR BUSYR ZQ0R[10] PORTSTD0R LOWSPDR VSS CQ0R CQ0R VSS

TDI

TDO DNU DNU

Y DNU DNU VSS

VSS DNU DQ17L DQ14L DQ11L DQ8L

DQ5L DQ2L DQ2R DQ5R DQ8R DQ11R DQ14R DQ17R DNU TMS

TCK DNU DNU

AA DNU DNU DNU DNU DNU DQ16L DQ13L DQ10L DQ7L DQ4L DQ1L DQ1R DQ4R DQ7R DQ10R DQ13R DQ16R DNU DNU DNU DNU DNU

AB DNU DNU DNU DNU DNU DQ15L DQ12L DQ9L DQ6L DQ3L DQ0L DQ0R DQ3R DQ6R DQ9R DQ12R DQ15R DNU DNU DNU DNU DNU

Notes

9. Use this pinout only for device CYD36S36V18 of the FullFlex36 family.

10. Leave this ball unconnected to disable VIM.

Document Number: 38-06082 Rev. *O

Page 5 of 53

5 Page

CYDXXS72V18

CYDXXS36V18

CYDXXS18V18

Selectable IO Standard

The FullFlex device families offer the option to choose one of the

four port standards for the device. Each port independently

selects standards from single ended HSTL class I, single ended

LVTTL, 2.5 V LVCMOS, or 1.8 V LVCMOS. The selection of the

standard is determined by the PORTSTD pins for each port.

These pins must be connected to an LVTTL power suppy. This

determines the input clock, address, control, data, and Echo

clock standard for each port as shown in Table 1.

Table 1. Port Standard Selection

PORTSTD1

VSS

VSS

VTTL

VTTL

PORTSTD0

VSS

VTTL

VSS

VTTL

I/O Standard

LVTTL

HSTL

2.5 V LVCMOS

1.8 V LVCMOS

Clocking

Separate clocks synchronize the operations on each port. Each

port has one clock input C. In this mode, all the transactions on

the address, control, and data are on the C rising edge. All

transactions on the address, control, data input, output, and byte

enables occur on the C rising edge.

Table 2. Data Pin Assignment

BE Pin Name

BE[7]

BE[6]

BE[5]

BE[4]

BE[3]

BE[2]

BE[1]

BE[0]

Data Pin Name

DQ[71:63]

DQ[62:54]

DQ[53:45]

DQ[44:36]

DQ[35:27]

DQ[26:18]

DQ[17:9]

DQ[8:0]

Selectable Pipelined or Flow through Mode

To meet data rate and throughput requirements, the FullFlex

families offer selectable pipelined or flow through mode. Echo

clocks are not supported in flow through mode and the DLL must

be disabled.

Flow through mode is selected by the FTSEL pin. Strapping this

pin HIGH selects pipelined mode. Strapping this pin LOW selects

flow through mode.

DLL

The FullFlex familes of devices have an on-chip DLL. Enabling

the DLL reduces the clock to data valid (tCD) time enabling more

setup time for the receiving device. In flow through mode, the

DLL must be disabled. This is selectable by strapping LowSPD

low.

Whenever the operating frequency is altered beyond the Clock

Input Cycle to Cycle Jitter specification, reset the DLL, followed

by 1024 clocks before any valid operation.

LowSPD pins are used to reset the DLLs for a single port

independent of all other circuitry. MRST is used to reset all DLLs

on the chip. For more information on DLL lock and reset time,

see Master Reset on page 18.

Echo Clocking

As the speed of data increases, on-board delays caused by

parasitics make it extremely difficult to provide accurate clock

trees. To counter this problem, the FullFlex families incorporate

Echo Clocks. Echo Clocks are enabled on a per port basis. The

dual port receives input clocks that are used to clock in the

address and control signals for a read operation. The dual port

retransmits the input clocks relative to the data output. The

buffered clocks are provided on the CQ1/CQ1 and CQ0/CQ0

outputs. Each port has a pair of Echo clocks. Each clock is

associated with half the data bits. The output clock matches the

corresponding ports IO configuration.

To enable echo clock outputs, tie CQEN HIGH. To disable echo

clock outputs, tie CQEN LOW.

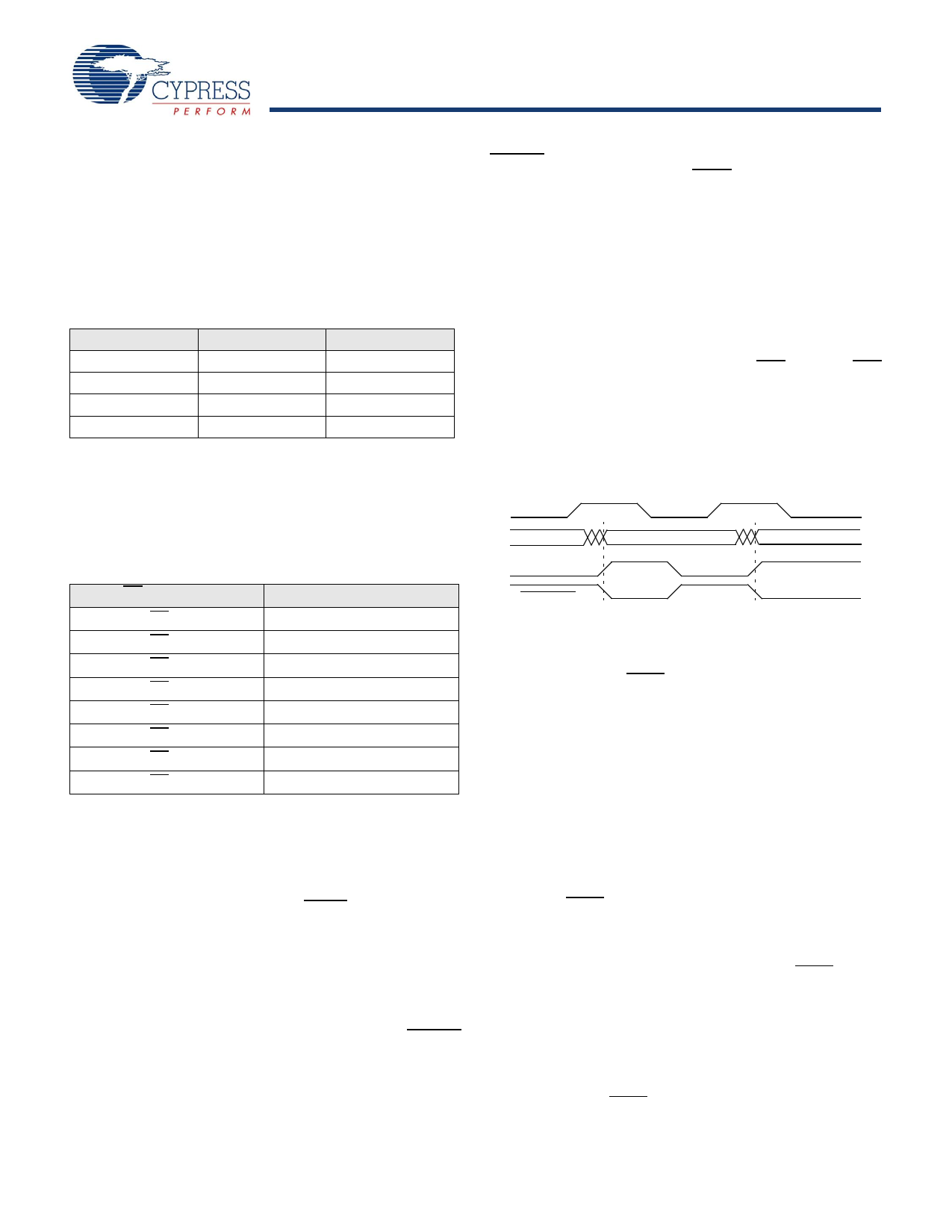

Figure 6. SDR Echo Clock Delay

Input Clock

Data Out

Echo Clock

Echo Clock

Deterministic Access Control

Deterministic Access Control is provided for ease of design. The

circuitry detects when both ports access the same location and

provides an external BUSY flag to the port on which data is

corrupted. The collision detection logic saves the address in

conflict (Busy Address) to a readable register. In the case of

multiple collisions, the first busy address is written to the busy

address register.

If both ports access the same location at the same time and only

one port is doing a write, if tCCS is met, then the data written to

and read from the address is valid data. For example, if the right

port is reading and the left port is writing and the left ports clock

meets tCCS, then the data read from the address by the right port

is the old data. In the same case, if the right ports clock meets

tCCS, then the data read out of the address from the right port is

the new data. In the above case, if tCCS is violated by the either

ports clock with respect to the other port and the right port gets

the external BUSY flag, the data from the right port is corrupted.

Table 3 on page 12 shows the tCCS timing that must be met to

guarantee the data.

Table 4 on page 12 shows that, in the case of the left port writing

and the right port reading, when an external BUSY flag is

asserted on the right port, the data read out of the device is not

guaranteed.

The value in the busy address register is read back to the

address lines. The required input control signals for this function

are shown in Table 7 on page 14. The value in the busy address

register is read out to the address lines tCA after the same

amount of latency as a data read operation. After an initial

address match, the BUSY flag is asserted and the address under

contention is saved in the busy address register. All the following

Document Number: 38-06082 Rev. *O

Page 11 of 53

http://www.Datasheet4U.com

11 Page | ||

| Páginas | Total 30 Páginas | |

| PDF Descargar | [ Datasheet CYD02S36V18.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| CYD02S36V18 | Dual Port SRAM | Cypress Semiconductor |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |