|

|

PDF 64F7058 Data sheet ( Hoja de datos )

| Número de pieza | 64F7058 | |

| Descripción | HD64F7058 | |

| Fabricantes | Renesas | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de 64F7058 (archivo pdf) en la parte inferior de esta página. Total 70 Páginas | ||

|

No Preview Available !

REJ09B0046-0300H

The revision list can be viewed directly by

clicking the title page.

The rivision list summarizes the locations of

revisions and additions. Details should always

be checked by referring to the relevant text.

32

SH-2E SH7058 F-ZTAT TM

Hardware Manual

Renesas SuperHTM RISC engine

Rev. 3.00

Revision date: Sep. 17, 2004

www.renesas.com

Free Datasheet http://www.datasheet4u.com/

1 page

SH7058 F-ZTAT manuals:

Manual Title

SH7058 F-ZTAT Hardware Manual

SH-2E Programming Manual

Document No.

This manual

Users manuals for development tools:

Manual Title

SH Series C/C++ Compiler, Assembler, Optimizing Linkage Editor User's

Manual

SH Series Simulator/Debugger (for Windows) User's Manual

SH Series Simulator/Debugger (for UNIX) User's Manual

High-performance Embedded Workshop User's Manual

Document No.

ADE-702-246

ADE-702-186

ADE-702-203

ADE-702-201

Application note:

Manual Title

C/C++ Compiler

Document No.

Rev. 3.0, 09/04, page ii of xxxviii

Free Datasheet http://www.datasheet4u.com/

5 Page

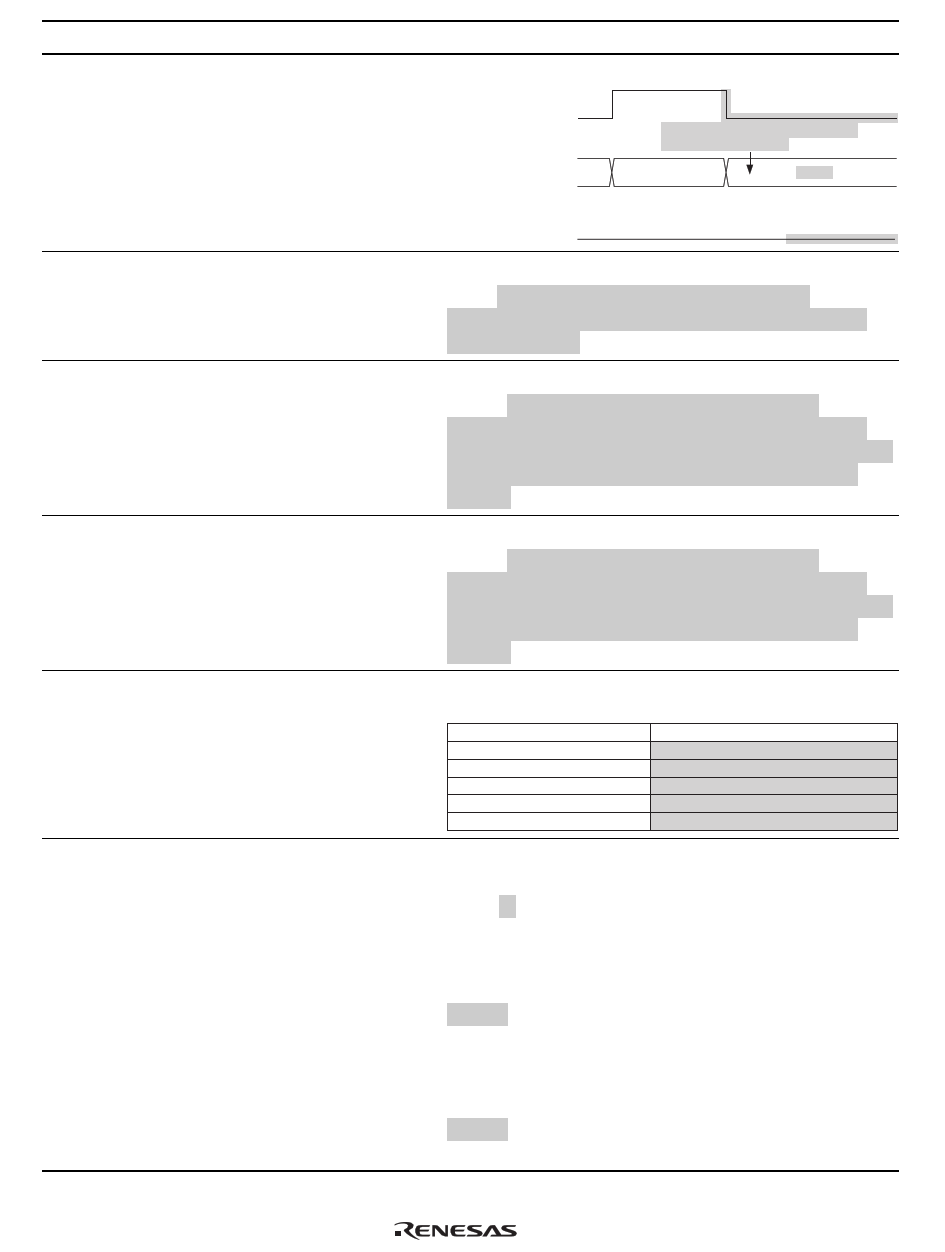

Item

Page Revisions (See Manual for Details)

11.7 Usage Notes

420 Figure amended

Figure 11.72 Contention between DCNT

Write and Underflow

Underflow signal

H'5555 is written because DCNT

write is given priority

DCNT 0001

0000

5555

12.1.4 Register Configuration

Table 12.2 Advanced Pulse Controller

Register

429

14.1.3 Register Configuration

Table 14.1 Register Configuration

453

15.1.4 Register Configuration

Table 15.2 Registers

467

Section 16 Controller Area Network-II 519-

(HCAN-II)

616

16.1.1 Features

519,

520

Interrupt status flag

(OSF)

Note amended

Note: Register access with an internal clock

multiplication ratio of 4 requires four or five internal

clock (φ) cycles.

Note amended

Notes: Register access with an internal clock

multiplication ratio of 4 requires four or five internal

clock (φ) cycles for byte access and word access, and

eight or nine internal clock (φ) cycles for longword

access.

Note amended

Notes: Register access with an internal clock

multiplication ratio of 4 requires four or five internal

clock (φ) cycles for byte access and word access, and

eight or nine internal clock (φ) cycles for longword

access.

Description amended

Register name

Before

HCAN-II_bit configuration register

Transmit wait register

Transmit wait cancel register

Receive complete register

Remote request register

After

HCAN-II_bit timing configuration register

Transmit Pending Request Register

Transmit Cancel Register

Data Frame Receive Pending Register

Remote Frame Receive Pending Register

Description amended

• Supports CAN specification 2.0A/2.0B and ISO-

11898-1

Description deleted

• Flexible interrupt structure

• Read section 16.8, Usage Notes carefully.

The following features have been added in the HCAN-

II.

• IRR0 function to notify a software reset and halt

Rev. 3.0, 09/04, page viii of xxxviii

Free Datasheet http://www.datasheet4u.com/

11 Page | ||

| Páginas | Total 70 Páginas | |

| PDF Descargar | [ Datasheet 64F7058.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| 64F7054 | HD64F7054 | Renesas Technology |

| 64F7055 | HD64F7055 | Renesas Technology |

| 64F7058 | HD64F7058 | Renesas |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |