|

|

PDF LTC1856 Data sheet ( Hoja de datos )

| Número de pieza | LTC1856 | |

| Descripción | 100ksps ADC Converters | |

| Fabricantes | Linear Technology | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de LTC1856 (archivo pdf) en la parte inferior de esta página. Total 24 Páginas | ||

|

No Preview Available !

FEATURES

■ Single 5V Supply

■ Sample Rate: 100ksps

■ 8-Channel Multiplexer with ±30V Protection

■ ±10V Bipolar Input Range

Single Ended or Differential

■ ±3LSB INL for the LTC1856, ±1.5LSB INL for the

www.DaLtTaCSh1e8e5t54U,.±co1mLSB INL for the LTC1854

■ Power Dissipation: 40mW (Typ)

■ SPI/MICROWIRETM Compatible Serial I/O

■ Power Shutdown: Nap and Sleep

■ SINAD: 87dB (LTC1856)

■ Operates with Internal or External Reference

■ Internal Synchronized Clock

■ 28-Pin SSOP Package

U

APPLICATIO S

■ Industrial Process Control

■ Multiplexed Data Acquisition Systems

■ High Speed Data Acquisition for PCs

■ Digital Signal Processing

LTC1854/LTC1855/LTC1856

8-Channel, ±10V Input

12-/14-/16-Bit, 100ksps ADC

Converters with Shutdown

DESCRIPTIO

The LTC®1854/LTC1855/LTC1856 are 8-channel, low

power, 12-/14-/16-bit, 100ksps, analog-to-digital con-

verters (ADCs). These ADCs operate from a single 5V

supply and the 8-channel multiplexer can be programmed

for single-ended inputs, pairs of differential inputs, or

combinations of both. In addition, all channels are fault

protected to ±30V. A fault condition on any channel will

not affect the conversion result of the selected channel.

An onboard precision reference minimizes external com-

ponents. Power dissipation is 40mW at 100ksps and lower

in two power shutdown modes (27.5mW in Nap mode and

40mW in Sleep mode.) DC specifications include ±3LSB

INL for the LTC1856, ±1.5LSB INL for the LTC1855 and

±1LSB for the LTC1854.

The internal clock is trimmed for 5ms maximum conver-

sion time and the sampling rate is guaranteed at 100ksps.

A separate convert start input and data ready signal (BUSY)

ease connections to FIFOs, DSPs and microprocessors.

, LT, LTC and LTM are registered trademarks of Linear Technology Corporation.

All other trademarks are the property of their respective owners.

TYPICAL APPLICATIO

100kHz, 12-Bit/14-/16-Bit Sampling ADC

SOFTWARE-PROGRAMMABLE

SINGLE-ENDED OR

DIFFERENTIAL INPUTS

±10V BIPOLAR INPUT RANGE

COM

CONVST

CH0 LTC1854/ RD

CH1 LTC1855/ SCK

CH2 LTC1856 SDI

CH3 DGND

CH4 SDO

CH5 BUSY

CH6 OVDD

CH7

MUXOUT+

MUXOUT–

DVDD

AVDD

AGND3

ADC+

AGND2

ADC–

REFCOMP

AGND1

VREF

μP

CONTROL

LINES

0.1μF

10μF

10μF

0.1μF

10μF

1μF 10μF 0.1μF

3V TO 5V

5V

5V

0.1μF

2.5V

LTC1856 Typical INL Curve

2.0

1.5

1.0

0.5

0

–0.5

–1.0

–1.5

–2.0

–32768 –16384

0

CODE

16384 32767

185456 G01

185456fa

1

1 page

LTC1854/LTC1855/LTC1856

WU

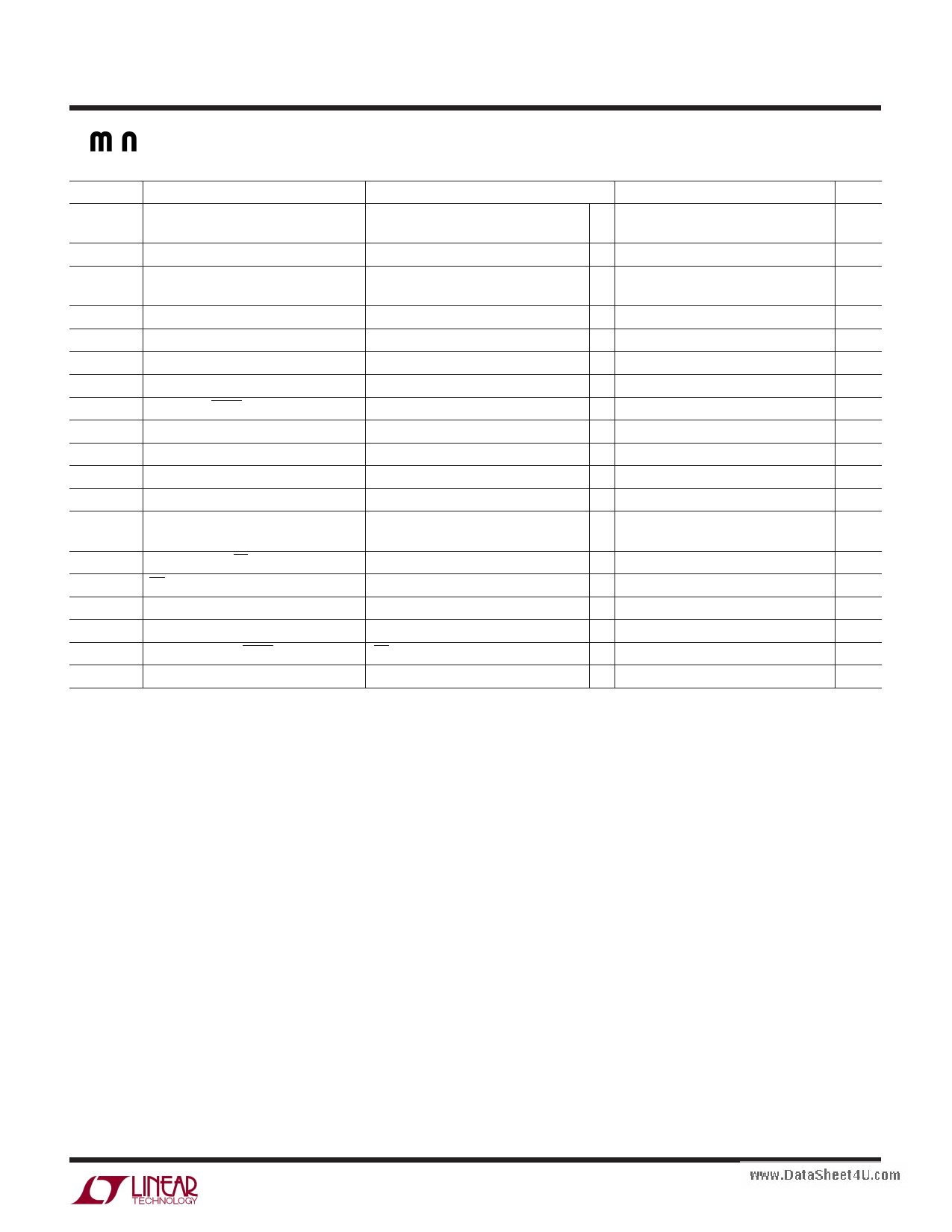

TI I G CHARACTERISTICS The ● denotes the specifications which apply over the full operating temperature

range, otherwise specifications are at TA = 25∞C. (Note 5)

SYMBOL PARAMETER

CONDITIONS

MIN TYP MAX UNITS

fSAMPLE(MAX) Maximum Sampling Frequency

Through CH0 to CH7 Inputs

Through ADC+, ADC– Only

● 100

166

kHz

kHz

tCONV

Conversion Time

● 4 5 ms

tACQ Acquisition Time

Through CH0 to CH7 Inputs

Through ADC+, ADC– Only

●

4 ms

1 ms

fSCK SCK Frequency

(Note 13)

●0

20 MHz

tr SDO Rise Time

See Test Circuits

6 ns

tf SDO Fall Time

See Test Circuits

6 ns

wwwt1.DataSheet4CUO.cNoVmST High Time

t2 CONVST to BUSY Delay

CL = 25pF, See Test Circuits

● 40

● 15 30

ns

ns

t3 SCK Period

● 50

ns

t4 SCK High

● 10

ns

t5 SCK Low

● 10

ns

t6

Delay Time, SCKØ to SDO Valid

CL = 25pF, See Test Circuits

●

25 45

ns

t7 Time from Previous SDO Data Remains CL = 25pF, See Test Circuits

Valid After SCKØ

●5

20

ns

t8 SDO Valid After RDØ

CL = 25pF, See Test Circuits

●

11 30

ns

t9 RDØ to SCK Setup Time

● 20

ns

t10 SDI Setup Time Before SCK≠

●0

ns

t11 SDI Hold Time After SCK≠

●7

ns

t12 SDO Valid Before BUSY≠

RD = Low, CL = 25pF, See Test Circuits ●

5

20

ns

t13 Bus Relinquish Time

See Test Circuits

●

10 30

ns

Note 1: Stresses beyond those listed under Absolute Maximum Ratings

may cause permanent damage to the device. Exposure to any Absolute

Maximum Rating condition for extended periods may affect device

reliability and lifetime.

Note 2: All voltage values are with respect to ground with DGND, AGND1,

AGND2 and AGND3 wired together unless otherwise noted.

Note 3: When these pin voltages are taken below ground or above AVDD =

DVDD = OVDD = VDD, they will be clamped by internal diodes. This product

can handle currents of greater than 100mA below ground or above VDD

without latchup.

Note 4: When these pin voltages are taken below ground they will be

clamped by internal diodes. This product can handle currents of greater

than 100mA below ground without latchup. These pins are not clamped

to VDD.

Note 5: VDD = 5V, fSAMPLE = 100kHz, tr = tf = 5ns unless otherwise

specified.

Note 6: Linearity, offset and full-scale specifications apply for a single-

ended analog MUX input with respect to ground or ADC+ with respect to

ADC– tied to ground.

Note 7: Integral nonlinearity is defined as the deviation of a code from a

straight line passing through the actual end points of the transfer curve.

The deviation is measured from the center of the quantization band.

Note 8: Bipolar zero error is the offset voltage measured from – 0.5LSB

when the output code flickers between 0000 0000 0000 0000 and 1111

1111 1111 1111 for the LTC1856, between 00 0000 0000 0000 and 11

1111 1111 1111 for the LTC1855 and between 0000 0000 0000 and 1111

1111 1111 for the LTC1854.

Note 9: Guaranteed by design, not subject to test.

Note 10: Recommended operating conditions.

Note 11: Full-scale bipolar error is the worst case of –FS or +FS

untrimmed deviation from ideal first and last code transitions, divided by

the full-scale range, and includes the effect of offset error.

Note 12: Recovers to specified performance after (2 • FS) input

overvoltage.

Note 13: t6 of 45ns maximum allows fSCK up to 10MHz for rising capture

with 50% duty cycle and fSCK up to 20MHz for falling capture (with 5ns

setup time for the receiving logic).

185456fa

5

5 Page

TEST CIRCUITS

Load Circuits for Access Timing

DN

1k

25pF

5V

1k

DN

25pF

(A) Hi-Z TO VOH AND VOL TO VOH

(B) Hi-Z TO VOL AND VOH TO VOL

18545 TC01

www.DataSheet4U.com

TI I G DIAGRA S

CONVST

t1 (For Short Pulse Mode)

t1

50% 50%

18545 TD01

t3, t4, t5 (SCK Timing)

t4 t5

SCK

t3 18545 TD03

t8 (SDO Valid After RD )

t8

RD 0.4V

Hi-Z

SDO

2.4V

0.4V

18545 TD05

LTC1854/LTC1855/LTC1856

Load Circuits for Output Float Delay

DN

1k

25pF

5V

1k

DN

25pF

(A) VOH TO Hi-Z

(B) VOL TO Hi-Z

18545 TC02

CONVST

t2 (CONVST to BUSY Delay)

t2

2.4V

BUSY

0.4V

18545 TD02

t6 (Delay Time, SCK to SDO Valid)

t7 (Time from Previous Data Remains Valid After SCK )

t6

t7

SCK 0.4V

SDO

2.4V

0.4V

18545 TD04

t9 (RD to SCK Setup Time)

t9

RD 0.4V

SCK

2.4V

18545 TD06

185456fa

11

11 Page | ||

| Páginas | Total 24 Páginas | |

| PDF Descargar | [ Datasheet LTC1856.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| LTC1850 | 1.25Msps Sampling ADCs | Linear Technology |

| LTC1851 | 1.25Msps Sampling ADCs | Linear Technology |

| LTC1852 | Sampling ADCs | Linear Technology |

| LTC1853 | Sampling ADCs | Linear Technology |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |