No Preview Available !

www.DataSheet4U.com

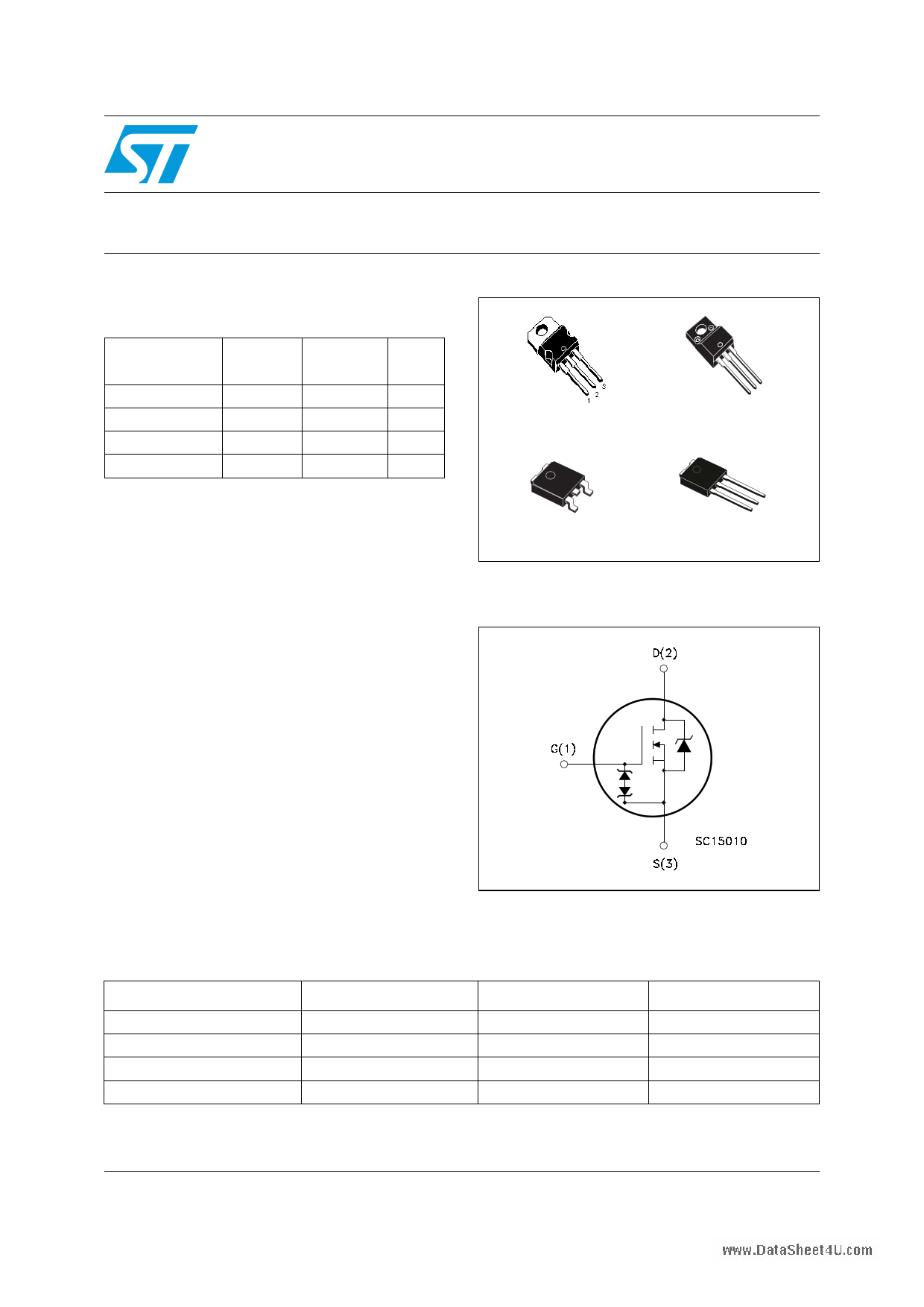

STP3NK80Z - STF3NK80Z

STD3NK80Z - STD3NK80Z-1

N-channel 800V - 3.8Ω - 2.5A - TO-220/TO-220FP/DPAK/IPAK

Zener-protected SuperMESH™ Power MOSFET

General features

Type

STP3NK80Z

STF3NK80Z

STD3NK80Z

STD3NK80Z-1

VDSS

(@Tjmax)

800 V

800 V

800 V

800 V

RDS(on)

< 4.5 Ω

< 4.5 Ω

< 4.5 Ω

< 4.5 Ω

ID

2.5 A

2.5 A

2.5 A

2.5 A

■ Extremely high dv/dt capability

■ 100% avalanche tested

■ Gate charge minimized

■ Very low intrinsic capacitances

■ Very good manufacturing repeatibility

Description

The SuperMESH™ series is obtained through an

extreme optimization of ST’s well established

strip-based PowerMESH™ layout. In addition to

pushing on-resistance significantly down, special

care is taken to ensure a very good dv/dt

capability for the most demanding applications.

Such series complements ST full range of high

voltage MOSFETs including revolutionary

MDmesh™ products.

Applications

■ Switching application

TO-220

3

2

1

TO-220FP

3

1

DPAK

IPAK

3

2

1

Internal schematic diagram

Order codes

Part number

STP3NK80Z

STF3NK80Z

STD3NK80ZT4

STD3NK80Z-1

Marking

P3NK80Z

F3NK80Z

D3NK80Z

D3NK80Z

Package

TO-220

TO-220FP

DPAK

IPAK

Packaging

Tube

Tube

Tape & reel

Tube

August 2006

Rev 4

1/18

www.st.com

18

1 page

www.DataSShTeePt43UN.cKo8m0Z - STF3NK80Z - STD3NK80Z - STD3NK80Z-1

2 Electrical characteristics

Electrical characteristics

(TCASE=25°C unless otherwise specified)

Table 5. On/off states

Symbol

Parameter

Test conditions

V(BR)DSS

Drain-source breakdown

voltage

ID = 1mA, VGS= 0

IDSS

Zero gate voltage drain

current (VGS = 0)

VDS = Max rating,

VDS = Max rating,

Tc = 125°C

IGSS

VGS(th)

RDS(on)

Gate body leakage current

(VGS = 0)

VGS = ± 20V

Gate threshold voltage

VDS = VGS, ID = 50µA

Static drain-source on

resistance

VGS = 10V, ID = 1.25 A

Min. Typ. Max. Unit

800 V

1 µA

50 µA

±10 µA

3 3.75 4.5

V

3.8 4.5 Ω

Table 6. Dynamic

Symbol

Parameter

Test conditions

Min. Typ. Max. Unit

gfs (1)

Ciss

Coss

Crss

Forward transconductance VDS =15V, ID = 1.25A

Input capacitance

Output capacitance

Reverse transfer

capacitance

VDS =25V, f=1 MHz, VGS=0

2.1

485

57

11

S

pF

pF

pF

Cosseq(2).

Equivalent output

capacitance

VGS=0, VDS =0V to 640V

22

pF

td(on)

tr

td(off)

tf

Turn-on delay time

Rise time

Off-voltage rise time

Fall time

VDD=400 V, ID= 1.25 A,

RG=4.7Ω, VGS=10V

(see Figure 18)

17 ns

27 ns

36 ns

40 ns

Qg Total gate charge

Qgs Gate-source charge

Qgd Gate-drain charge

VDD=640V, ID = 2.5 A

VGS =10V

19 nC

3.2 nC

10.8 nC

1. Pulsed: pulse duration=300µs, duty cycle 1.5%

2. Coss eq. is defined as a constant equivalent capacitance giving the same charging time as Coss when VDS

increases from 0 to 80% VDSS

5/18

5 Page

www.DataSShTeePt43UN.cKo8m0Z - STF3NK80Z - STD3NK80Z - STD3NK80Z-1

4 Package mechanical data

Package mechanical data

In order to meet environmental requirements, ST offers these devices in ECOPACK®

packages. These packages have a Lead-free second level interconnect . The category of

second level interconnect is marked on the package and on the inner box label, in

compliance with JEDEC Standard JESD97. The maximum ratings related to soldering

conditions are also marked on the inner box label. ECOPACK is an ST trademark.

ECOPACK specifications are available at: www.st.com

11/18

11 Page

|