|

|

PDF 25L8005 Data sheet ( Hoja de datos )

| Número de pieza | 25L8005 | |

| Descripción | MX25L8005 | |

| Fabricantes | MXIC | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de 25L8005 (archivo pdf) en la parte inferior de esta página. Total 42 Páginas | ||

|

No Preview Available !

PRELIMINARY

MX25L4005, MX25L8005

FEATURES

GENERAL

• Serial Peripheral Interface (SPI) compatible -- Mode 0

and Mode 3

• 4,194,304 x 1 bit structure for 4M; 8,388,608 x 1 bit

structure for 8M

www.DataSheet•4U1.2co8mEqual Sectors with 4K byte each (MX25L4005)

256 Equal Sectors with 4K byte each (MX25L8005)

- Any Sector can be erased individually

• 8 Equal Blocks with 64K byte each (MX25L4005)

16 Equal Blocks with 64K byte each (MX25L8005)

- Any Block can be erased individually

• Single Power Supply Operation

- 2.7 to 3.6 volt for read, erase, and program operations

• Latch-up protected to 100mA from -1V to Vcc +1V

• Low Vcc write inhibit is from 1.5V to 2.5V

PERFORMANCE

• High Performance

- Fast access time: 70MHz serial clock (15pF + 1TTL

Load) and 66MHz serial clock (30pF + 1TTL Load)

- Fast program time: 1.4ms(typ.) and 5ms(max.)/page

(256-byte per page)

- Fast erase time: 90ms(typ.) and 270ms(max.)/sector

(4K-byte per sector) ; 1s(typ.) and 3s(max.)/block (64K-

byte per block)

• Low Power Consumption

- Low active read current: 12mA(max.) at 70MHz,

8mA(max.) at 66MHz and 4mA(max.) at 33MHz

- Low active programming current: 30mA (max.)

- Low active erase current: 15mA (max.)

- Low standby current: 50uA (max.)

- Deep power-down mode 1uA (typical)

• Minimum 100,000 erase/program cycles

4M/8M-BIT [x 1] CMOS SERIAL FLASH

SOFTWARE FEATURES

• Input Data Format

- 1-byte Command code

• Block Lock protection

- The BP0~BP2 status bit defines the size of the area

to be software protected against Program and Erase

instructions.

• Auto Erase and Auto Program Algorithm

- Automatically erases and verifies data at selected

sector

- Automatically programs and verifies data at selected

page by an internal algorithm that automatically times

the program pulse widths (Any page to be programed

should have page in the erased state first)

• Status Register Feature

• Electronic Identification

- JEDEC 2-byte Device ID

- RES command, 1-byte Device ID

HARDWARE FEATURES

• SCLK Input

- Serial clock input

• SI Input

- Serial Data Input

• SO Output

- Serial Data Output

• WP# pin

- Hardware write protection

• HOLD# pin

- pause the chip without diselecting the chip

• PACKAGE

- 8-pin SOP (150mil)

- 8-pin SOP (200mil)

- 8-land SON (6x5mm)

P/N: PM1130

REV. 0.04, MAY. 31, 2005

1

1 page

MX25L4005, MX25L8005

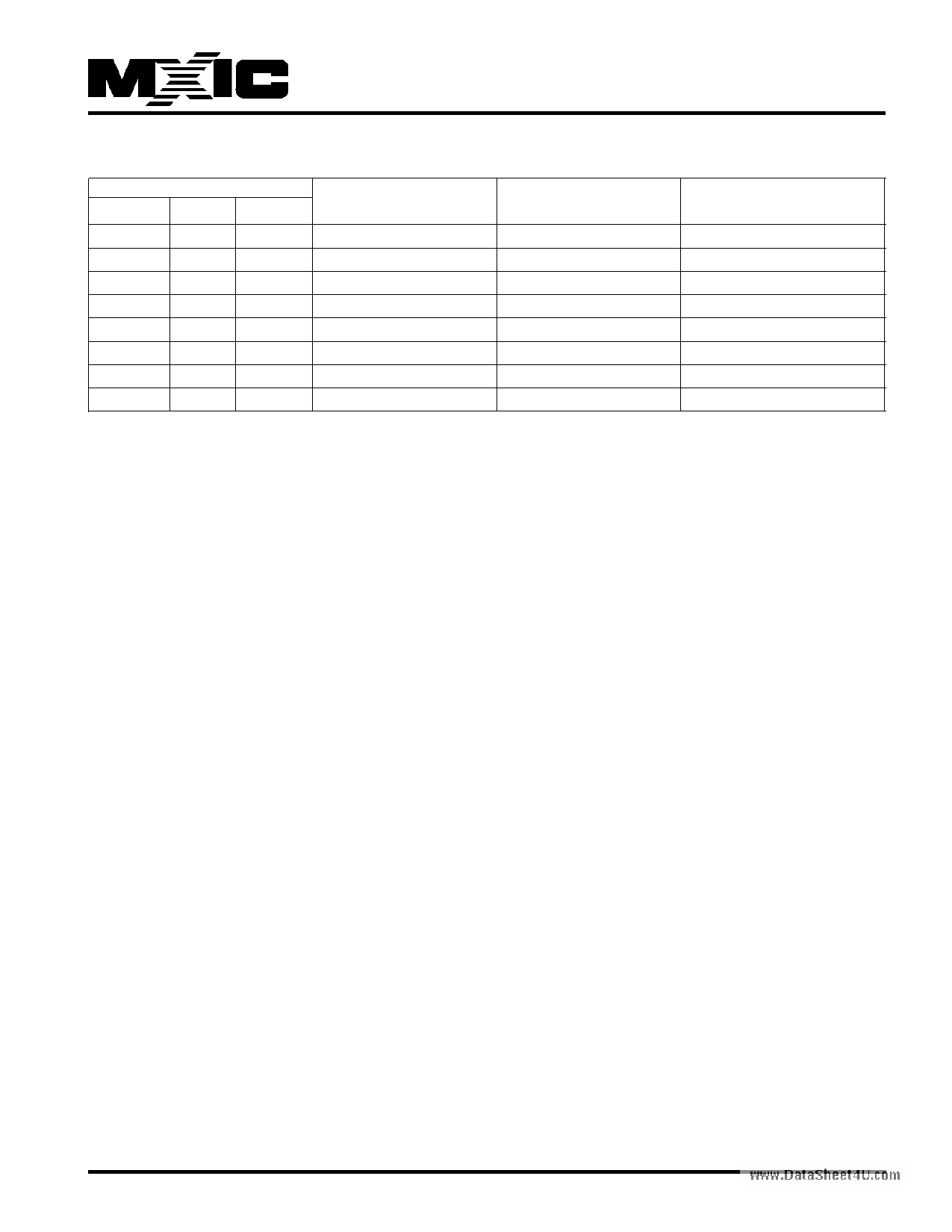

Table 1. Protected Area Sizes

Status bit

BP2 BP1 BP0

000

001

010

011

100

www.DataSheet4U.com1 0 1

110

111

Protect level

0 (none)

1 (1 block)

2 (2 blocks)

3 (4 blocks)

4 (8 blocks)

5 (All)

6 (All)

7 (All)

4Mb

None

Block 7

Block 6-7

Block 4-7

All

All

All

All

8Mb

None

Block 15

Block 14-15

Block 12-15

Block 8-15

All

All

All

P/N: PM1130

REV. 0.04, MAY. 31, 2005

5

5 Page

MX25L4005, MX25L8005

(4) Read Status Register (RDSR)

The RDSR instruction is for reading Status Register Bits. The Read Status Register can be read at any time (even in

program/erase/write status register condition) and continuously. It is recommended to check the Write in Progress (WIP)

bit before sending a new instruction when a program, erase, or write status register operation is in progress.

The sequence of issuing RDSR instruction is: CS# goes low-> sending RDSR instruction code-> Status Register data out

on SO (see Figure. 14)

The definition of the status register bits is as below:

www.DataSheetW4UI.Pcobmit. The Write in Progress (WIP) bit, a volatile bit, indicates whether the device is busy in program/erase/write status

register progress. When WIP bit sets to 1, which means the device is busy in program/erase/write status register progress.

When WIP bit sets to 0, which means the device is not in progress of program/erase/write status register cycle.

WEL bit. The Write Enable Latch (WEL) bit, a volatile bit, indicates whether the device is set to internal write enable latch.

When WEL bit sets to 1, which means the internal write enable latch is set, the device can accept program/erase/write

status register instruction. When WEL bit sets to 0, which means no internal write enable latch; the device will not accept

program/erase/write status register instruction.

BP2, BP1, BP0 bits. The Block Protect (BP2, BP1, BP0) bits, non-volatile bits, indicate the protected area(as defined

in table 1) of the device to against the program/erase instruction without hardware protection mode being set. To write the

Block Protect (BP2, BP1, BP0) bits requires the Write Status Register (WRSR) instruction to be executed. Those bits

define the protected area of the memory to against Page Program (PP), Sector Erase (SE), Block Erase (BE) and Chip

Erase(CE) instructions (only if all Block Protect bits set to 0, the CE instruction can be executed)

SRWD bit. The Status Register Write Disable (SRWD) bit, non-volatile bit, is operated together with Write Protection (WP#)

pin for providing hardware protection mode. The hardware protection mode requires SRWD sets to 1 and WP# pin signal

is low stage. In the hardware protection mode, the Write Status Register (WRSR) instruction is no longer accepted for

execution and the SRWD bit and Block Protect bits (BP2, BP1, BP0) are read only.

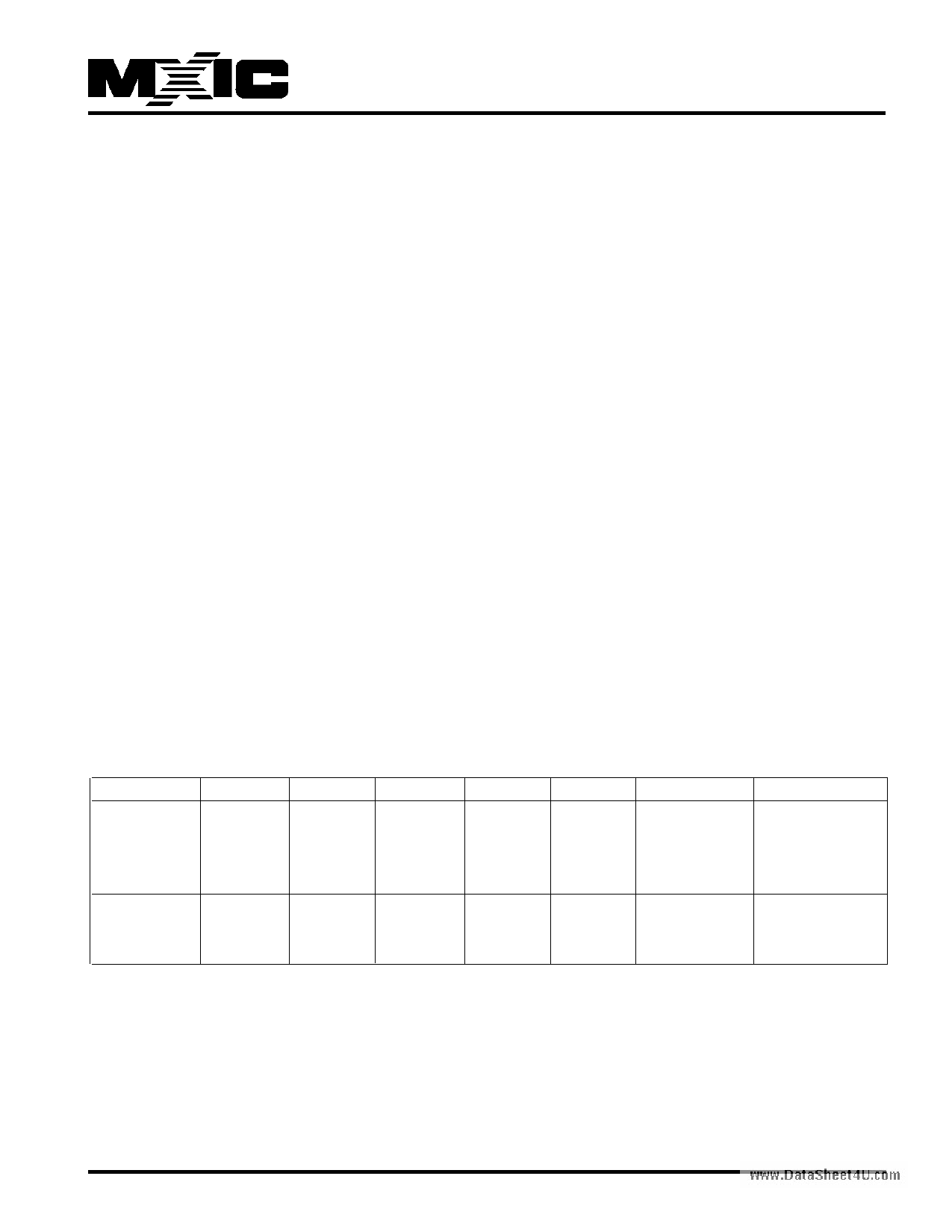

bit 7

SRWD

Status

Register Write

Protect

1= status

register write

disable

bit 6

0

bit 5 bit 4 bit 3 bit 2

bit 1

bit 0

BP2 BP1 BP0

WEL

WIP

0 the level of the level of the level of (write enable (write in progress

protected protected protected

latch)

bit)

block

block

block

(note 1) (note 1) (note 1) 1=write enable 1=write operation

0=not write 0=not in write

enable

operation

Note: 1. see the table "Protected Area Sizes"

P/N: PM1130

REV. 0.04, MAY. 31, 2005

11

11 Page | ||

| Páginas | Total 42 Páginas | |

| PDF Descargar | [ Datasheet 25L8005.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| 25L8005 | MX25L8005 | MXIC |

| 25L8006E | MX25L8006E | MXIC |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |