|

|

PDF LTC2624 Data sheet ( Hoja de datos )

| Número de pieza | LTC2624 | |

| Descripción | (LTC2604 - LTC2624) Rail-to-rail Voltage Output DACs | |

| Fabricantes | Linear Technology | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de LTC2624 (archivo pdf) en la parte inferior de esta página. Total 16 Páginas | ||

|

No Preview Available !

LTC2604/LTC2614/LTC2624

Quad 16-Bit Rail-to-Rail DACs

in 16-Lead SSOP

FEATURES

s Smallest Pin Compatible Quad 16-Bit DAC:

LTC2604: 16-Bits

LTC2614: 14-Bits

LTC2624: 12-Bits

s Guaranteed 16-Bit Monotonic Over Temperature

s Separate Reference Inputs for each DAC

s Wide 2.5V to 5.5V Supply Range

s Low Power Operation: 250µA per DAC at 3V

s Individual DAC Power-Down to 1µA, Max

s Ultralow Crosstalk Between DACs (<5µV)

s High Rail-to-Rail Output Drive (±15mA)

s Double Buffered Digital Inputs

s 16-Lead Narrow SSOP Package

U

APPLICATIO S

www.DataSheet4U.com

s

Mobile

Communications

s Process Control and Industrial Automation

s Instrumentation

s Automatic Test Equipment

BLOCK DIAGRA

GND

1

REF LO

2

REF A

3

VOUTA

4

DAC A

VOUTB

5

REF B

6

CS/LD

7

SCK

8

DAC B

CONTROL

LOGIC

DECODE

32-BIT SHIFT REGISTER

DESCRIPTIO

The LTC®2604/LTC2614/LTC2624 are quad 16-,14- and

12-bit 2.5V to 5.5V rail-to-rail voltage output DACs in

16-lead narrow SSOP packages. These parts have sepa-

rate reference inputs for each DAC. They have built-in

high performance output buffers and are guaranteed

monotonic.

These parts establish advanced performance standards

for output drive, crosstalk and load regulation in single-

supply, voltage output multiples.

The parts use a simple SPI/MICROWIRETM compatible

3-wire serial interface which can be operated at clock

rates up to 50MHz. Daisy-chain capability and a hardware

CLR function are included.

The LTC2604/LTC2614/LTC2624 incorporate a power-

on reset circuit. During power-up, the voltage outputs

rise less than 10mV above zero scale; and after power-

up, they stay at zero scale until a valid write and update

take place.

, LTC and LT are registered trademarks of Linear Technology Corporation.

MICROWIRE is a trademark of National Semiconductor Corp.

DAC D

VCC

16

REF D

15

VOUT D

14

DAC C

VOUT C

13

REF C

12

CLR

11

SDO

10

SDI

9

2604 BD

Differential Nonlinearity (LTC2604)

1.0

VCC = 5V

0.8 VREF = 4.096V

0.6

0.4

0.2

0

–0.2

–0.4

–0.6

–0.8

–1.0

0

16384

32768

CODE

49152 65535

2604 TA01

2604f

1

1 page

LTC2604/LTC2614/LTC2624

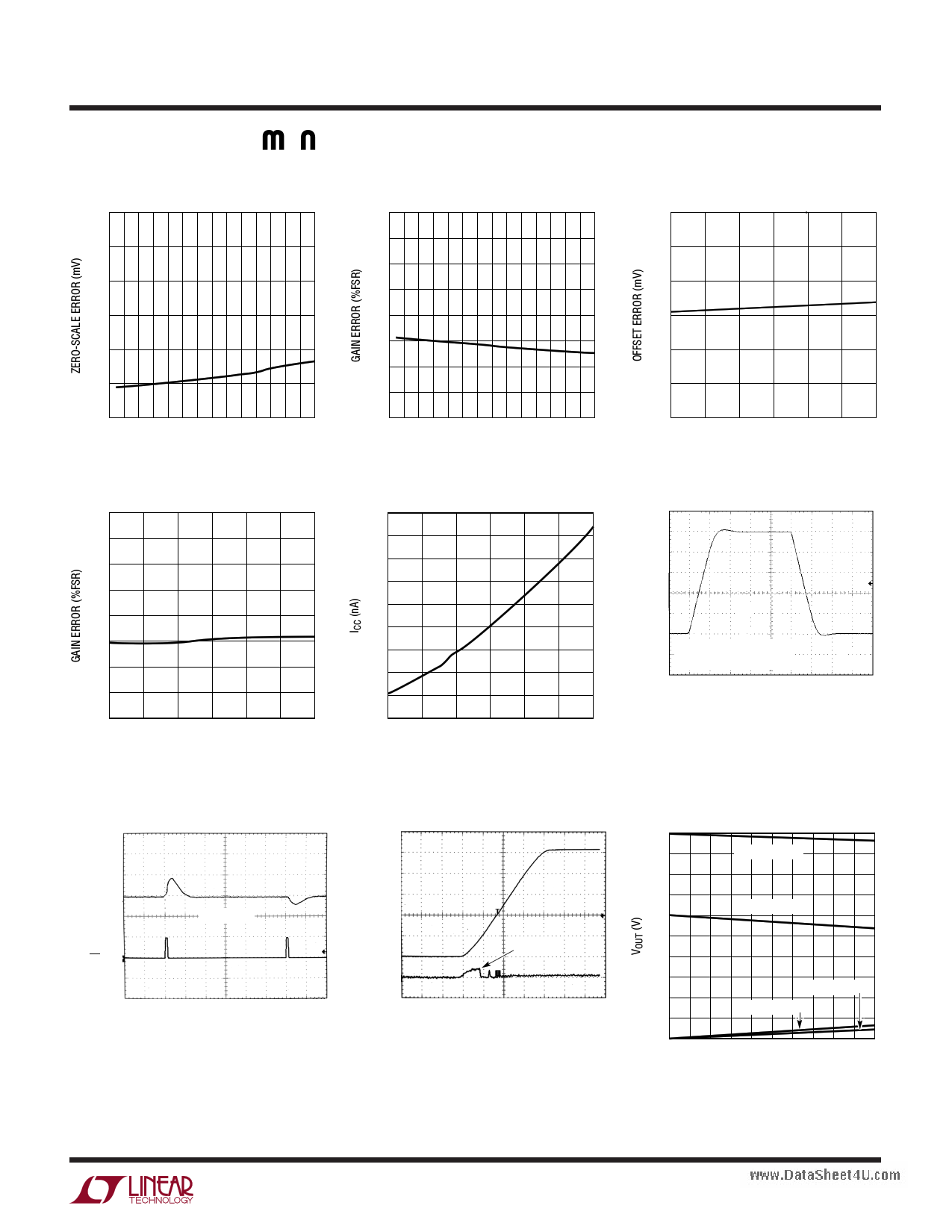

TYPICAL PERFOR A CE CHARACTERISTICS (LTC2604/LTC2614/LTC2624)

Zero-Scale Error vs Temperature

3

2.5

2.0

1.5

1.0

0.5

0

–50 –30 –10 10 30 50

TEMPERATURE (°C)

70 90

2604 G04

Gain Error vs VCC

0.4

0.3

0.2

0.1

www.DataSheet4U.com 0

–0.1

–0.2

–0.3

–0.4

2.5 3 3.5 4 4.5

VCC (V)

5 5.5

2604 G07

Gain Error vs Temperature

0.4

0.3

0.2

0.1

0

–0.1

–0.2

–0.3

–0.4

–50 –30 –10 10 30 50

TEMPERATURE (°C)

70 90

2604 G05

ICC Shutdown vs VCC

450

400

350

300

250

200

150

100

50

0

2.5 3 3.5 4 4.5

VCC (V)

5 5.5

2604 G08

Offset Error vs VCC

3

2

1

0

–1

–2

–3

2.5 3 3.5 4 4.5

VCC (V)

Large-Signal Settling

VOUT

0.5V/DIV

VREF = VCC = 5V

1/4-SCALE TO 3/4-SCALE

2.5µs/DIV

5 5.5

2604 G06

2604 G09

Midscale Glitch Impulse

Power-On Reset Glitch

VOUT

10mV/DIV

CS/LD

5V/DIV

12nV-s TYP

2.5µs/DIV

VCC

1V/DIV

2604 G10

VOUT

10mV/DIV

44mmVVPPEEAAKK

250µs/DIV

2604 G11

Headroom at Rails vs Output

Current

5.0

4.5 5V SOURCING

4.0

3.5

3V SOURCING

3.0

2.5

2.0

1.5

5V SINKING

1.0

3V SINKING

0.5

0

0 1 2 3 4 5 6 7 8 9 10

IOUT (mA)

2604 G12

2604f

5

5 Page

U

OPERATIO

LTC2604/LTC2614/LTC2624

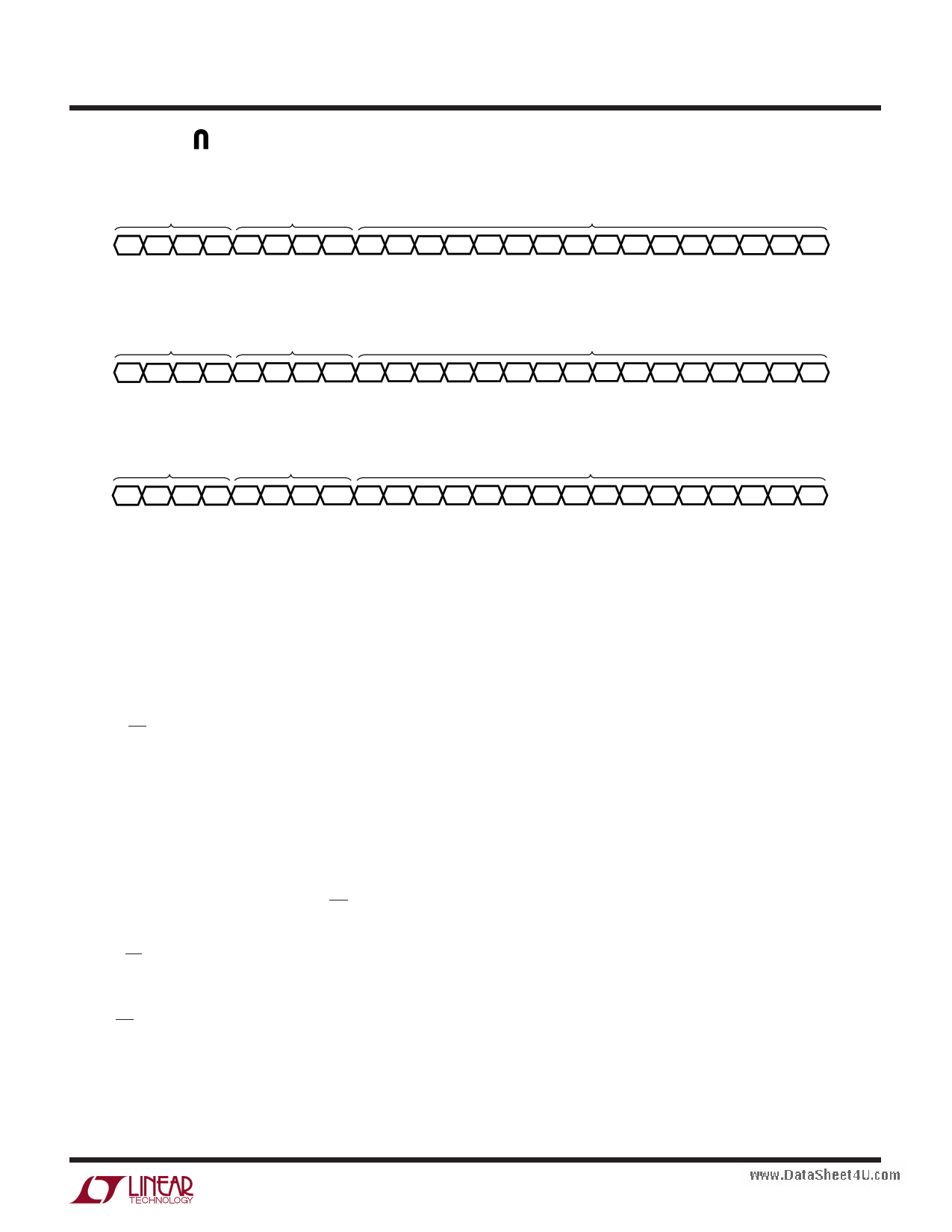

INPUT WORD (LTC2604)

COMMAND

ADDRESS

DATA (16 BITS)

C3 C2 C1 C0 A3 A2 A1 A0 D15 D14 D13 D12 D11 D10 D9 D8 D7 D6 D5 D4 D3 D2 D1 D0

MSB

LSB

2604 TBL01

INPUT WORD (LTC2614)

COMMAND

ADDRESS

DATA (14 BITS + 2 DON’T-CARE BITS)

C3 C2 C1 C0 A3 A2 A1 A0 D13 D12 D11 D10 D9 D8 D7 D6 D5 D4 D3 D2 D1 D0 X X

MSB

LSB

2604 TBL02

INPUT WORD (LTC2624)

COMMAND

ADDRESS

DATA (12 BITS + 4 DON’T-CARE BITS)

C3 C2 C1 C0 A3 A2 A1 A0 D11 D10 D9 D8 D7 D6 D5 D4 D3 D2 D1 D0 X X X X

MSB

LSB

2604 TBL03

Daisy-Chain Operation

The serial output of the shift register appears at the SDO

pin.www.DataSheet4U.com Data transferred to the device from the SDI input is

delayed 32 SCK rising edges before being output at the

next SCK falling edge.

The SDO output can be used to facilitate control of multiple

serial devices from a single 3-wire serial port (i.e., SCK,

SDI and CS/LD). Such a “daisy chain” series is configured

by connecting SDO of each upstream device to SDI of the

next device in the chain. The shift registers of the devices

are thus connected in series, effectively forming a single

input shift register which extends through the entire chain.

Because of this, the devices can be addressed and con-

trolled individually by simply concatenating their input

words; the first instruction addresses the last device in the

chain and so forth. The SCK and CS/LD signals are

common to all devices in the series.

In use, CS/LD is first taken low. Then the concatenated

input data is transferred to the chain, using SDI of the first

device as the data input. When the data transfer is com-

plete, CS/LD is taken high, completing the instruction

sequence for all devices simultaneously. A single device

can be controlled by using the no-operation command

(1111) for the other devices in the chain.

Power-Down Mode

For power-constrained applications, power-down mode

can be used to reduce the supply current whenever less

than four outputs are needed. When in power-down, the

buffer amplifiers, bias circuits and reference inputs are

disabled, and draw essentially zero current. The DAC

outputs are put into a high-impedance state, and the

output pins are passively pulled to ground through indi-

vidual 90k resistors. Input- and DAC-register contents are

not disturbed during power-down.

Any channel or combination of channels can be put into

power-down mode by using command 0100b in combina-

tion with the appropriate DAC address, (n). The 16-bit data

word is ignored. The supply current is reduced by approxi-

mately 1/4 for each DAC powered down. The effective

resistance at REF x (pins 3, 6, 12 and 15) are at high-

impedance input (typically > 1GΩ) when the correspond-

ing DACs are powered down.

Normal operation can be resumed by executing any com-

mand which includes a DAC update, as shown in Table 1.

The selected DAC is powered up as its voltage output is

updated. When a DAC which is in a powered-down state is

powered up and updated, normal settling is delayed. If less

than four DACs are in a powered-down state prior to the

update command, the power-up delay time is 5µs. If on the

2604f

11

11 Page | ||

| Páginas | Total 16 Páginas | |

| PDF Descargar | [ Datasheet LTC2624.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| LTC2620 | (LTC2600 - LTC2620) 3V/5V Octal 12-bit Rail-to-rail DAC | Linear Technology |

| LTC2621 | (LTC2601 - LTC2621) 12-Bit Rail-to-rail DACs | Linear Technology |

| LTC2622 | (LTC2602 - LTC2622) Rail-to-rail DACs | Linear Technology |

| LTC2624 | (LTC2604 - LTC2624) Rail-to-rail Voltage Output DACs | Linear Technology |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |