|

|

PDF CE6313 Data sheet ( Hoja de datos )

| Número de pieza | CE6313 | |

| Descripción | DVB-S Satellite Demodulator | |

| Fabricantes | Intel | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de CE6313 (archivo pdf) en la parte inferior de esta página. Total 24 Páginas | ||

|

No Preview Available !

www.DataSheet4U.com

CE6313

DVB-S Satellite Demodulator

Data Sheet

Features

• Conforms to EBU specification for DVB-S and

DirecTV specification for DSS

• On-chip digital filtering supports 1 - 45 MSps

symbol rates

• On-chip 60 or 90 MHz dual-ADC

• High speed scanning mode for blind symbol

rate/code rate acquisition

• Automatic spectral inversion resolution

• High level software interface for minimum

development time

• Up to ±22.5 MHz LNB frequency tracking

• DiSEqC™ v2.2: receive/transmit for full control of

LNB, dish and other components

• Compact 64-pin LQFP package (7 x 7 mm)

• A full DVB-S front-end reference design is

available, ref. CE9541

Applications

• DVB 1 - 45 MSps compliant satellite receivers

• DSS 20 MSps compliant satellite receivers

• SMATV (Single Master Antenna TV) trans-

modulators

• Satellite PC applications

May 2006

Ordering Information

DJCE6313 882131

WJCE6313 882207

64 Pin LQFP Trays

64 Pin LQFP* Trays

*Pb Free Matte Tin

0°C to +70°C

Description

The CE6313 is a QPSK/BPSK 1 - 45 MSps

demodulator and channel decoder for digital satellite

television transmissions to the European Broadcast

Union ETS 300 421 specification. It receives analogue

I and Q signals from the tuner, digitises and digitally

demodulates this signal, implements the complete

DVB/DSS FEC (Forward Error Correction) and de-

scrambling function. The output is in the form of

MPEG2 or DSS transport stream data packets. The

CE6313 also provides automatic gain control to the RF

front-end device.

The CE6313 has a serial 2-wire bus interface to the

control microprocessor. Minimal software is required to

control the CE6313 because of the built in automatic

search and decode control functions.

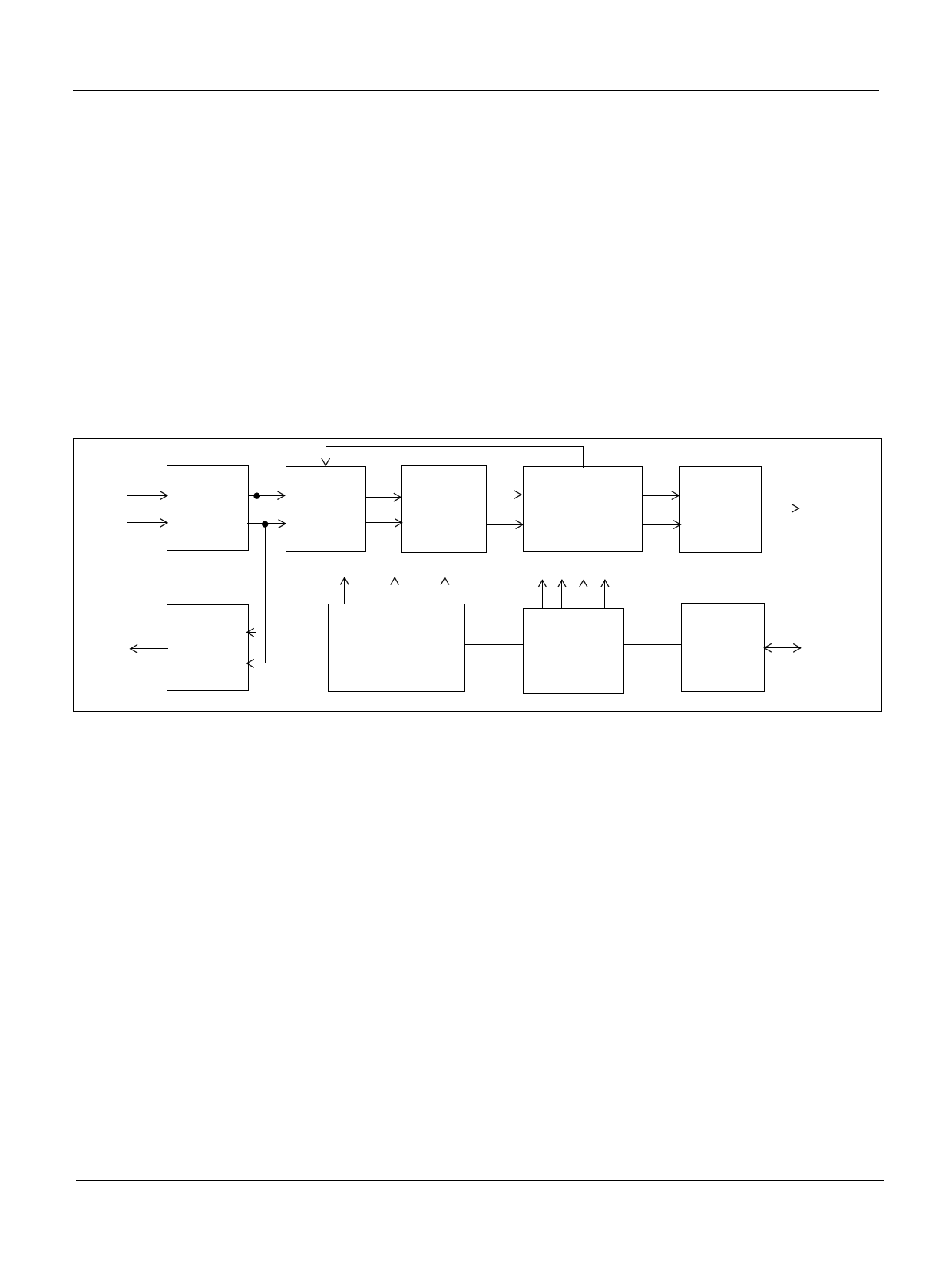

I I/P

Q I/P

Dual ADC

De-rotator

Decimation

Filtering

Timing recovery

Matched filter

Phase recovery

DVB

DSS

FEC

MPEG/

DSS

Packets

Analog

AGC

Control

Clock Generation

Acquisition

Control

2-Wire Bus Bus I/O

Interface

Figure 1 - Functional Block Diagram

www.DataSheet4U.com

1

Intel Corporation

D55751-001

Intel and the Intel logo are registered trademarks of Intel Corporation or its subsidiaries in the United States and other countries.

*Other names and brands may be claimed as the property of others. Copyright © 2006 Intel Corporation. All rights reserved.

1 page

www.DataSheet4U.com

CE6313

Data Sheet

Overview

The CE6313 is a QPSK/BPSK 1 - 45 MSps demodulator and channel decoder for digital satellite television

transmissions compliant to both DVB-S and DSS standards and other systems, such as LMDS, that use the same

architecture.

A Command Driven Control (CDC) system is provided making the CE6313 very simple to program. After the tuner

has been programmed to the required frequency to acquire a DVB transmission, the CE6313 requires a minimum

of five registers to be written.

The CE6313 provides a monitor of bit error rate after the QPSK module and also after the Viterbi module. For

receiver installation, a high speed scan or 'blind search' mode is available. This allows all signals from a given

satellite to be evaluated for frequency, symbol rate and convolutional coding scheme. The phase of the IQ signals

can be automatically determined.

Full DiSEqC is provided for both writing and reading DiSEqC messages. Storage in registers for up to eight data

bytes sent and eight data bytes received is provided.

I I/P

Q I/P

Dual ADC

De-rotator

Decimation

Filtering

Timing recovery

Matched filter

Phase recovery

DVB

DSS

FEC

MPEG/

DSS

Packets

Analog

AGC

Control

Clock Generation

Acquisition

Control

2-wire Bus Bus I/O

Interface

Figure 3 - CE6313 Functional Block Diagram

www.DataSheet4U.com

5

Intel Corporation

5 Page

www.DataSheet4U.com

VITERBI

Coarse

Bit

Error

Count

CE6313

Data Sheet

VIT_MAXERR[3:0]

0

0 Data Bits

Status

Figure 7 - Viterbi Error Count Coarse Indication

2.4.2 The Frame Alignment Block

The frame alignment algorithm detects a sequence of correctly spaced synchronizing bytes in the Viterbi decoded

bit-stream and arranges the input into blocks of data bytes. Each block consists of 204 bytes for DVB and 147 bytes

for DSS. In the DSS mode, the synchronizing byte is removed from the data stream, so only 146 bytes of a block

are passed to the next stage. The frame alignment block also removes the 180° phase ambiguity not removed by

the Viterbi decoder.

2.4.3 The De-Interleaver Block

2.4.3.1 DVB

Before transmission, the data bytes are interleaved with each other in a cyclic pattern of twelve. This ensures the

bytes are spaced out to avoid the possibility of a noise spike corrupting a group of consecutive message bytes.

Figure 8 below shows conceptually how the convolutional de-interleaving system works. The synchronization byte

is always loaded into the First-In-First-Out (FIFO) memory in branch 0. The switch is operated at regular byte

intervals to insert successively received bytes into successive branches. After 12 bytes have been received,

byte 13 is written next to the synchronization byte in branch 0, etc. In the CE6313, this de-interleaving function is

realized using on-chip Random Access Memory (RAM).

www.DataSheet4U.com

11

Intel Corporation

11 Page | ||

| Páginas | Total 24 Páginas | |

| PDF Descargar | [ Datasheet CE6313.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| CE6313 | DVB-S Satellite Demodulator | Intel |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |