|

|

PDF M12L128168A Data sheet ( Hoja de datos )

| Número de pieza | M12L128168A | |

| Descripción | Dynamic RAM | |

| Fabricantes | Elite Semiconductor | |

| Logotipo | ||

Hay una vista previa y un enlace de descarga de M12L128168A (archivo pdf) en la parte inferior de esta página. Total 30 Páginas | ||

|

No Preview Available !

ESMT

Revision History

M12L128168A

Revision 0.1 (Augut.30.1999)

- Original

Revision 0.2 (Jun.04.2002)

- Add DC characteristics

- Add -5, -6 speed grade

- Delete –8, -10, -12 speed grade

Revision 1.0 (Oct.31.2002)

- Delete “preliminary”

mRevision 1.1 (Mar.25.2003)

o- Modify DC characteristics

.cRevision 1.2 (Sep.02.2003)

U- Delete -5 speed grace

t4- Speed distribution -6 and -7

eRevision 1.3 (Aug.23.2004)

- M12L128168A -6T 125MHz : CL = 3(P7)

e- Correct polt2 clock suspend during read (P17)

h- Correct polt5 : tRDL(min) = 2clk (P20)

- Correct polt2 read interrupted by precharge

- Modify typing error of P18, P22, P23

taSRevision 1.4 (Oct.31.2002)

- Add Pb-free to ordering information

a- Modify P8 for bank precharge state to idle state

.DRevision 1.5 (Apr.22.2005)

- Modify refresh spec

wwRevision 1.6 (Jun.07.2005)

- Modify tREF spec (15.6μs refresh interval

w- Modify tRFC –7 spec (63ns 70ns)

64ms 4K)

Elite Semiconductor Memory Technology Inc.

Publication Date: Sep. 2005

Revision: 1.7

1/45

1 page

ESMT

M12L128168A

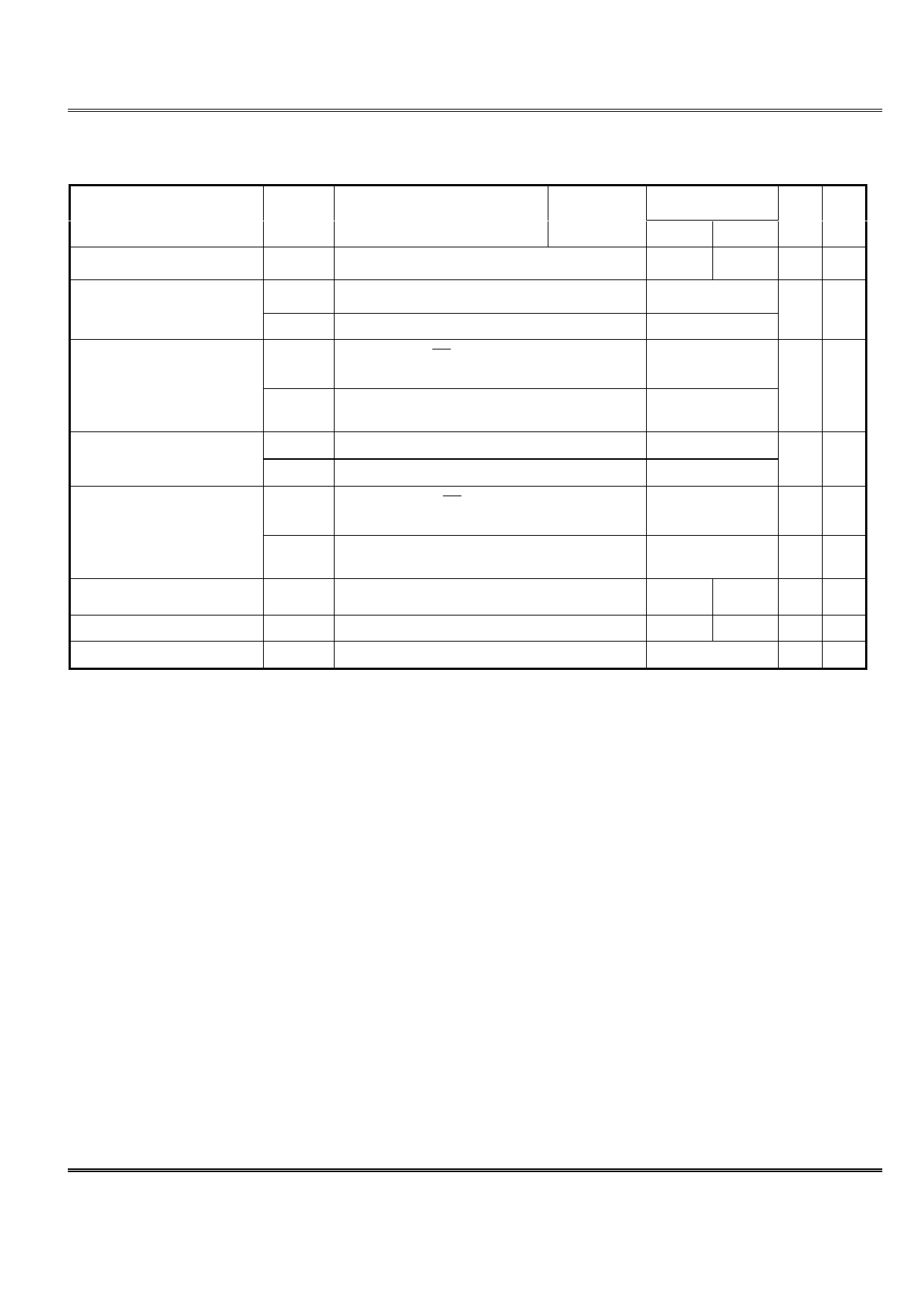

DC CHARACTERISTICS

Recommended operating condition unless otherwise noted,TA = 0 to 70 °C

Parameter

Symbol

Test Condition

CAS

Latency

Operating Current

(One Bank Active)

Precharge Standby Current

in power-down mode

ICC1

ICC2P

ICC2PS

Burst Length = 1, tRC ≥ tRC(min), IOL = 0 mA

CKE ≤ VIL(max), tcc = tCK(MIN)

CKE & CLK ≤ VIL (max), tCC = ∞

Precharge Standby Current

in non power-down mode

Active Standby Current

in power-down mode

ICC2N

ICC2NS

ICC3P

ICC3PS

CKE ≥ VIH(min), CS ≥ VIH(min), tCC = tCK(MIN)

Input signals are changed one time during 2tck

CKE ≥ VIH(min), CLK ≤ VIL(max), tcc = ∞

input signals are stable

CKE ≤ VIL(max), tCC = tCK(MIN)

CKE & CLK ≤ VIL(max), tCC = ∞

Active Standby Current

in non power-down mode

(One Bank Active)

Operating Current

(Burst Mode)

Refresh Current

Self Refresh Current

ICC3N

ICC3NS

ICC4

ICC5

ICC6

CKE ≥ VIH(min), CS ≥ VIH(min), tCC = tCK(MIN)

Input signals are changed one time during 2tCK

CKE ≥ VIH(min), CLK ≤ VIL(max), tCC = ∞

input signals are stable

IOL = 0 mA, Page Burst, 2 Banks activated

tRC ≥ tRC(min)

CKE ≤ 0.2V

Note : 1. Measured with outputs open.

2. Input signals are changed one time during 2 CLKS.

Version

-6 -7

160 140

2

2

45

25

6

6

55

Unit Note

mA 1,2

mA

mA

mA

mA

35

210 180

210 180

2

mA

mA 1,2

mA

mA

Elite Semiconductor Memory Technology Inc.

Publication Date: Sep. 2005

Revision: 1.7

5/45

5 Page

ESMT

M12L128168A

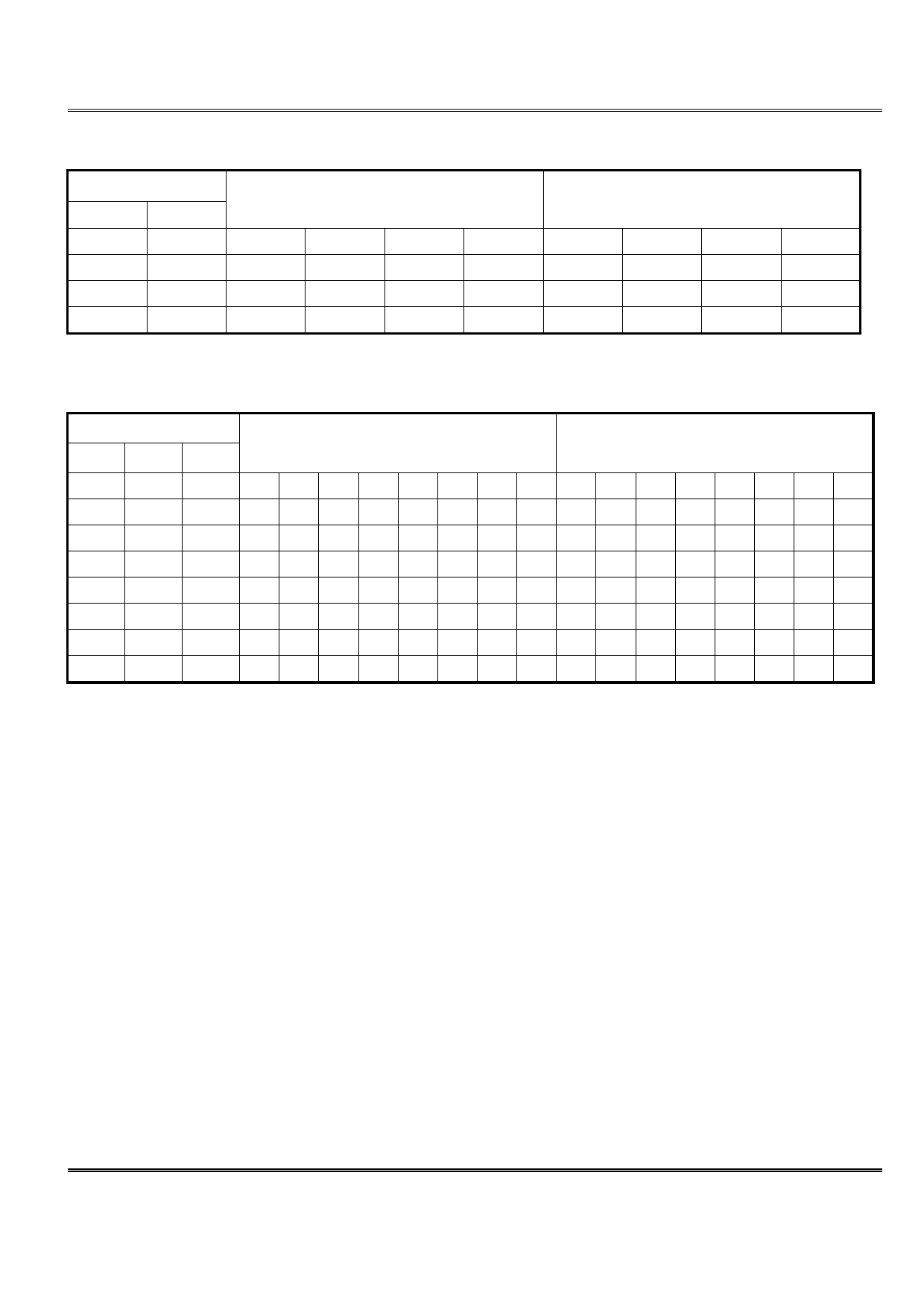

BURST SEQUENCE (BURST LENGTH = 4)

Initial Adrress

A1 A0

Sequential

Interleave

0001230123

0112301032

1023012301

1130123210

BURST SEQUENCE (BURST LENGTH = 8)

Initial

A2 A1 A0

Sequential

Interleave

0 0 0 0123456701234567

0 0 1 1234567010325476

0 1 0 2345670123016745

0 1 1 3456701232107654

1 0 0 4567012345670123

1 0 1 5670123454761032

1 1 0 6701234567452301

1 1 1 7012345676543210

Elite Semiconductor Memory Technology Inc.

Publication Date: Sep. 2005

Revision: 1.7

11/45

11 Page | ||

| Páginas | Total 30 Páginas | |

| PDF Descargar | [ Datasheet M12L128168A.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| M12L128168A | Dynamic RAM | Elite Semiconductor |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |