|

|

PDF ICS1572 Data sheet ( Hoja de datos )

| Número de pieza | ICS1572 | |

| Descripción | User Programmable Differential Output Graphics Clock Generator | |

| Fabricantes | Integrated Circuit Systems | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de ICS1572 (archivo pdf) en la parte inferior de esta página. Total 19 Páginas | ||

|

No Preview Available !

Integrated

Circuit

Systems, Inc.

ICS1572

User Programmable Differential Output Graphics Clock Generator

Description

The ICS1572 is a high performance monolithic phase-locked

loop (PLL) frequency synthesizer. Utilizing ICS’s advanced

CMOS mixed-mode technology, the ICS1572 provides a low

cost solution for high-end video clock generation in worksta-

tions and high-end PC applications.

The ICS1572 has differential video clock outputs (CLK+ and

CLK-) that are compatible with industry standard video DACs.

Another clock output, LOAD, is provided whose frequency is

derived from the main clock by a programmable divider. An

additional clock output is available, LD/N2, which is derived

from the LOAD frequency and whose modulus may also be

programmed.

Operating frequencies are fully programmable with direct con-

trol provided for reference divider, pre-scaler, feedback divider

and post-scaler.

Reset of the pipeline delay on Brooktree RAMDACs may

be performed under register control. Outputs may also be set

to desired states to facilitate circuit board testing.

Features

• Supports high-resolution graphics - CLK output to

180 MHz

• Eliminates need for multiple ECL output crystal oscillators

• Fully programmable synthesizer capability - not just a

clock multiplier

• Available in 20-pin 300-mil wide body SOIC package

• Available in both parallel (101) and serial (301)

programming versions

• Circuit included for reset of Brooktree RAMDAC pipeline

delay

Applications

• Workstations

• AutoCad Accelerators

• High-end PC graphics systems

ICS1572-101 Pinout

XTAL1

XTAL2

CRYSTAL

OSCILLATOR

EXTFBK (-301 only)

BLANK

PROGRAMMING

INTERFACE

/ R PHASE-

FREQUENCY

DETECTOR

MUX

CHARGE

PUMP

LOOP

FILTER

VCO

PRESCALER

/M /A

FEEDBACK DIVIDER

MUX

/2

/4

DIFF.

OUTPUT

/ N1

MUX

DRIVER

/ N2 DRIVER

N.C.

AD0

XTAL1

XTAL2

STROBE

VSS

VSS

LOAD

LD/N2

N.C.

1

2

3

4

5

6

7

8

9

10

20 N.C.

19 AD1

18 AD2

17 VDD

16 VDD

15 VDDO

14 IPRG

13 CLK+

12 CLK-

11 N.C.

CLK+

CLK−

LOAD

LD/N2

ICS1572-301 Pinout

N.C.

AD0

XTAL1

XTAL2

STROBE

VSS

VSS

LOAD

LD/N2

N.C.

1

2

3

4

5

6

7

8

9

10

20 N.C.

19 AD1

18 AD2

17 VDD

16 VDD

15 VDDO

14 IPRG

13 CLK+

12 CLK-

11 N.C.

Figure 1

ICS1572RevC093094

RAMDAC is a trademark of Brooktree Corporation.

1 page

ICS1572

Power-On Initialization

• Phase Detector Gain: For most graphics applications and

divider ranges, set P[1,0] = 10 and set P[2] = 1. Under

The ICS1572 has an internal power-on reset circuit that per-

some circumstances, setting the P[2] bit “on” can reduce

forms the following functions:

jitter. During 1572 operation at exact multiples of the

1) Sets the multiplexer to pass the reference frequency

to the CLK+ and CLK- outputs.

crystal frequency, P[2] bit = 0 may provide the best jitter

performance.

2) Selects the modulus of the N1 divider (for the

LOAD clock) to be four.

These functions should allow initialization of most graphics

systems that cannot immediately provide for register program-

ming upon system power-up.

Because the power-on reset circuit is on the VDD supply, and

because that supply is filtered, care must be taken to allow the

reset to de-assert before programming. A safe guideline is to

allow 20 microseconds after the VDD supply reaches 4 volts.

Board Test Support

It is often desirable to statically control the levels of the output

pins for circuit board test. The ICS1572 supports this through

a register programmable mode, AUXEN. When this mode is

set, two register bits directly control the logic levels of the

CLK+/CLK- pins and the LOAD pin. This mode is activated

when the S[0] and S[1] bits are both set to logic 1. See Register

Mapping for details.

Programming Notes

• VCO Frequency Range: Use the post-divider to keep the

VCO frequency as high as possible within its operating

range.

• Divider Range: For best results in normal situations (i.e.,

pixel clock generation for hi-res displays), keep the refer-

ence divider modulus as short as possible (for a frequency

at the output of the reference divider in the few hundred

kHz to several MHz range). If you need to go to a lower

phase comparator reference frequency (usually required

for increased frequency accuracy), that is acceptable, but

jitter performance will suffer somewhat.

• VCO Gain Programming: Use the minimum gain which

can reliably achieve the VCO frequency desired, as shown

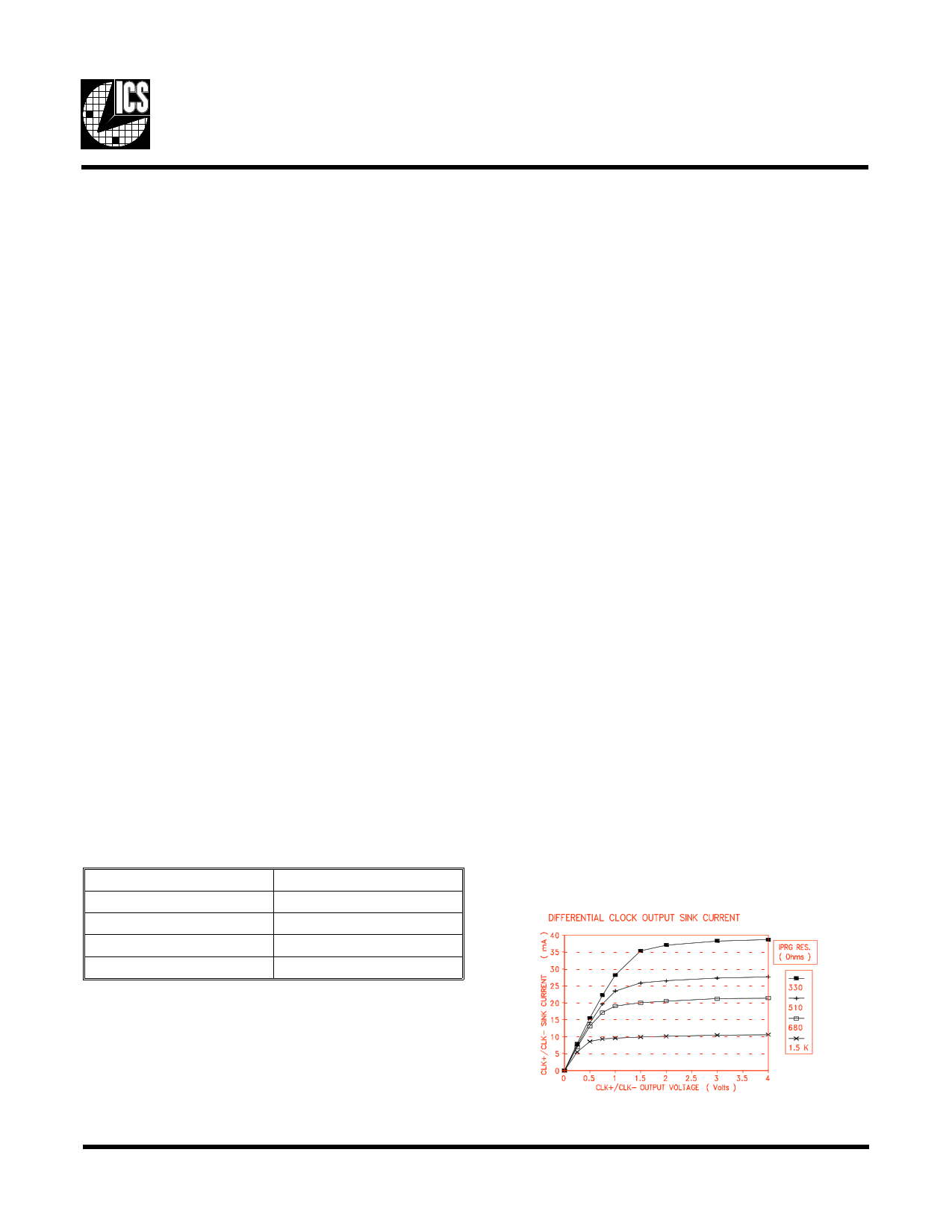

here:

VCO GAIN

4

5

6

7

MAX FREQUENCY

120 MHz

200 MHz

230 MHz

*

* SPECIAL APPLICATION. Contact factory for custom product above

230 MHz.

Power Supplies and Decoupling

The ICS1572 has two VSS pins to reduce the effects of package

inductance. Both pins are connected to the same potential on

the die (the ground bus). BOTH of these pins should connect

to the ground plane of the video board as close to the package

as is possible.

The ICS1572 has a VDDO pin which is the supply of +5 volt

power to all output drivers. This pin should be connected to the

power plane (or bus) using standard high-frequency decou-

pling practice. That is, capacitors should have low series induc-

tance and be mounted close to the ICS1572.

The VDD pin is the power supply pin for the PLL synthesizer

circuitry and other lower current digital functions. We recom-

mend that RC decoupling or zener regulation be provided for

this pin (as shown in the recommended application circuitry).

This will allow the PLL to “track” through power supply

fluctuations without visible effects. See Figure 7 for typical

external circuitry.

Figure 6

5

5 Page

BIT(S)

33-38

39

40

41-44

45-48

49-55

56

BIT REF.

M[0]..M[5]

RESERVED

DBLFREQ

A[0]..A[3]

RESERVED

R[0]..R[6]

RESERVED

ICS1572

DESCRIPTION

M counter control bits

Modulus = value +1

Set to zero.

Doubles modulus of dual-modulus prescaler (from 6/7 to 12/14).

Controls A counter. When set to zero, modulus=7. Otherwise,

modulus=7 for “value” underflows of the prescaler, and modulus=6

thereafter until M counter underflows.

Set to zero.

Reference divider modulus control bits

Modulus = value + 1

Set to zero.

11

11 Page | ||

| Páginas | Total 19 Páginas | |

| PDF Descargar | [ Datasheet ICS1572.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| ICS1572 | User Programmable Differential Output Graphics Clock Generator | Integrated Circuit Systems |

| ICS1574B | User Programmable Laser Engine Pixel Clock Generator | Integrated Circuit Systems |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |