|

|

PDF 28F008SA-L Data sheet ( Hoja de datos )

| Número de pieza | 28F008SA-L | |

| Descripción | 8-MBIT (1 MBIT x 8) FLASHFILETM MEMORY | |

| Fabricantes | Intel | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de 28F008SA-L (archivo pdf) en la parte inferior de esta página. Total 28 Páginas | ||

|

No Preview Available !

28F008SA-L

8-MBIT (1 MBIT x 8) FLASHFILETM MEMORY

Y High-Density Symmetrically-Blocked

Architecture

Sixteen 64-Kbyte Blocks

Y Low-Voltage Operation

b3 3V g0 3V or 5 0V g10% VCC

Y Extended Cycling Capability

10 000 Block Erase Cycles

160 000 Block Erase

Cycles per Chip

Y Automated Byte Write and Block Erase

Command User Interface

Status Register

Y System Performance Enhancements

RY BY Status Output

Erase Suspend Capability

Y High-Performance Read

200 ns Maximum Access Time

Y Deep Power-Down Mode

0 20 mA ICC Typical

Y SRAM-Compatible Write Interface

Y Hardware Data Protection Feature

Erase Write Lockout during Power

Transitions

Y Industry Standard Packaging

40-Lead TSOP 44-Lead PSOP

Y ETOXTM III Nonvolatile Flash

Technology

12V Byte Write Block Erase

Intel’s 28F008SA-L 8 Mbit FlashFileTM Memory is the highest density nonvolatile read write solution for solid-

state storage The 28F008SA-L’s extended cycling symmetrically-blocked architecture fast access time write

automation and very low power consumption provide a more reliable lower power lighter weight and higher

performance alternative to traditional rotating disk technology The 28F008SA-L brings new capabilities to

portable computing Application and operating system software stored in resident flash memory arrays provide

instant-on rapid execute-in-place and protection from obsolescence through in-system software updates

Resident software also extends system battery life and increases reliability by reducing disk drive accesses

For high-density data acquisition applications the 28F008SA-L offers a more cost-effective and reliable alter-

native to SRAM and battery Traditional high-density embedded applications such as telecommunications

can take advantage of the 28F008SA-L’s nonvolatility blocking and minimal system code requirements for

flexible firmware and modular software designs

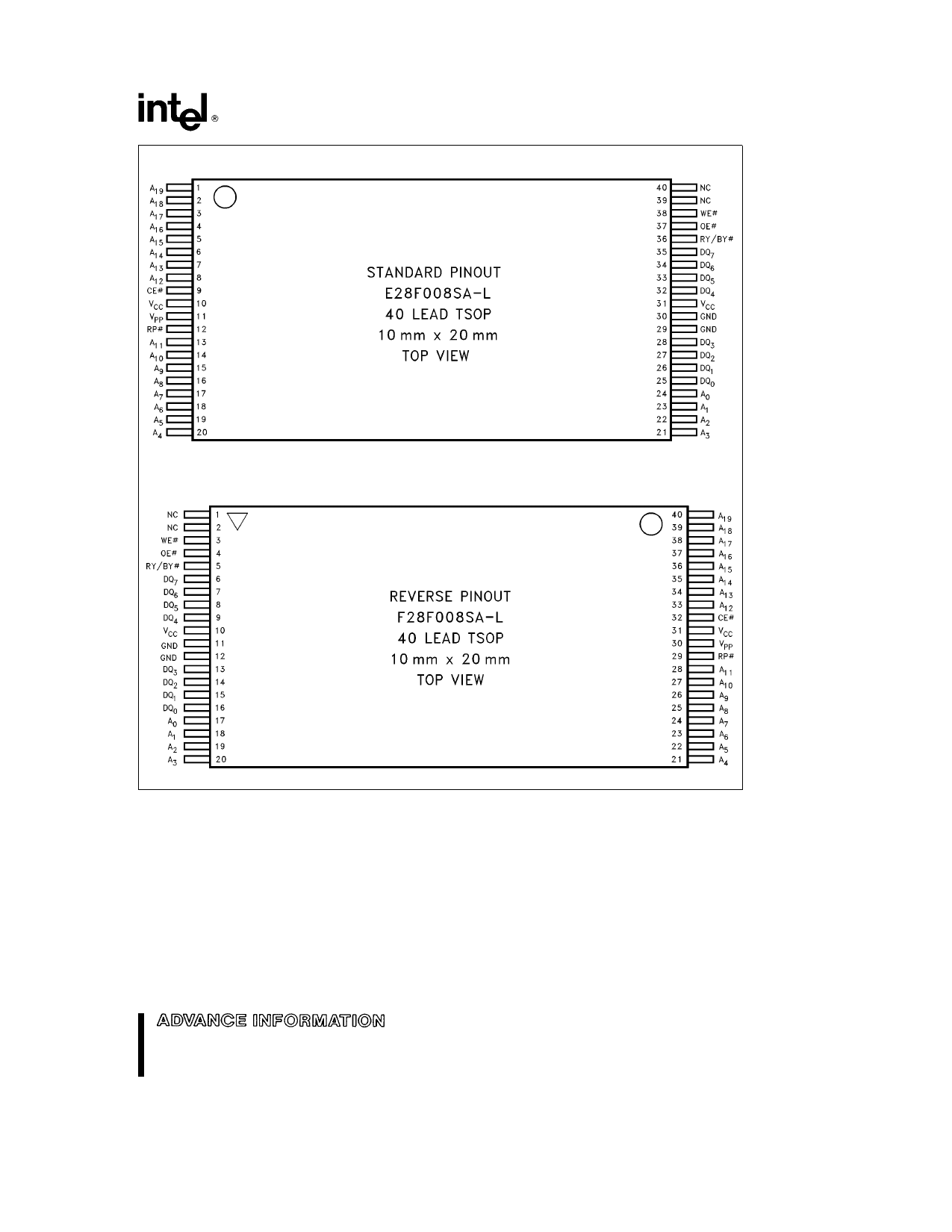

The 28F008SA-L is offered in 40-lead TSOP (standard and reverse) and 44-lead PSOP packages Pin assign-

ments simplify board layout when integrating multiple devices in a flash memory array or subsystem This

device uses an integrated Command User Interface and state machine for simplified block erasure and byte

write The 28F008SA-L memory map consists of 16 separately erasable 64-Kbyte blocks

Intel’s 28F008SA-L employs advanced CMOS circuitry for systems requiring low power consumption and

noise immunity Its 200 ns access time provides superior performance when compared with magnetic storage

media A deep power-down mode lowers power consumption to 0 66 mW typical thru VCC crucial in portable

computing handheld instrumentation and other low-power applications The RP power control input also

provides absolute data protection during system power-up down

Manufactured on Intel’s 0 8 micron ETOX process the 28F008SA-L provides the highest levels of quality

reliability and cost-effectiveness

Other brands and names are property of their respective owners

Other brands and names are the property of their respective owners

Information in this document is provided in connection with Intel products Intel assumes no liability whatsoever including infringement of any patent or

copyright for sale and use of Intel products except as provided in Intel’s Terms and Conditions of Sale for such products Intel retains the right to make

changes to these specifications at any time without notice Microcomputer Products may have minor variations to this specification known as errata

COPYRIGHT INTEL CORPORATION 1995

December 1995

Order Number 290435-005

1 page

Standard Pinout

28F008SA-L

Reverse Pinout

290435 – 2

Figure 2 TSOP Lead Configurations

290435 – 3

5

5 Page

28F008SA-L

Write

Writes to the Command User Interface enable read-

ing of device data and Intelligent Identifiers They

also control inspection and clearing of the Status

Register Additionally when VPP e VPPH the Com-

mand User Interface controls block erasure and byte

write The contents of the interface register serve as

input to the internal state machine

The Command User Interface itself does not occupy

an addressable memory location The interface reg-

ister is a latch used to store the command and ad-

dress and data information needed to execute the

command Erase Setup and Erase Confirm com-

mands require both appropriate command data and

an address within the block to be erased The Byte

Write Setup command requires both appropriate

command data and the address of the location to be

written while the Byte Write command consists of

the data to be written and the address of the loca-

tion to be written

The Command User Interface is written by bringing

WE to a logic-low level (VIL) while CE is low

Addresses and data are latched on the rising edge

of WE Standard microprocessor write timings are

used

COMMAND DEFINITIONS

When VPPL is applied to the VPP pin read opera-

tions from the Status Register Intelligent Identifiers

or array blocks are enabled Placing VPPH on VPP

enables successful byte write and block erase oper-

ations as well

Device operations are selected by writing specific

commands into the Command User Interface Table

3 defines the 28F008SA-L commands

Read Array Command

Upon initial device powerup and after exit from deep

powerdown mode the 28F008SA-L defaults to

Read Array mode This operation is also initiated by

writing FFH into the Command User Interface Mi-

croprocessor read cycles retrieve array data The

device remains enabled for reads until the Com-

mand User Interface contents are altered Once the

internal Write State Machine has started a block

erase or byte write operation the device will not rec-

ognize the Read Array command until the WSM has

completed its operation The Read Array command

is functional when VPP e VPPL or VPPH

Refer to AC Write Characteristics and the AC Wave-

forms for Write Operations Figure 11 for specific

timing parameters

Intelligent Identifier Command

The 28F008SA-L contains an Intelligent Identifier

operation initiated by writing 90H into the Command

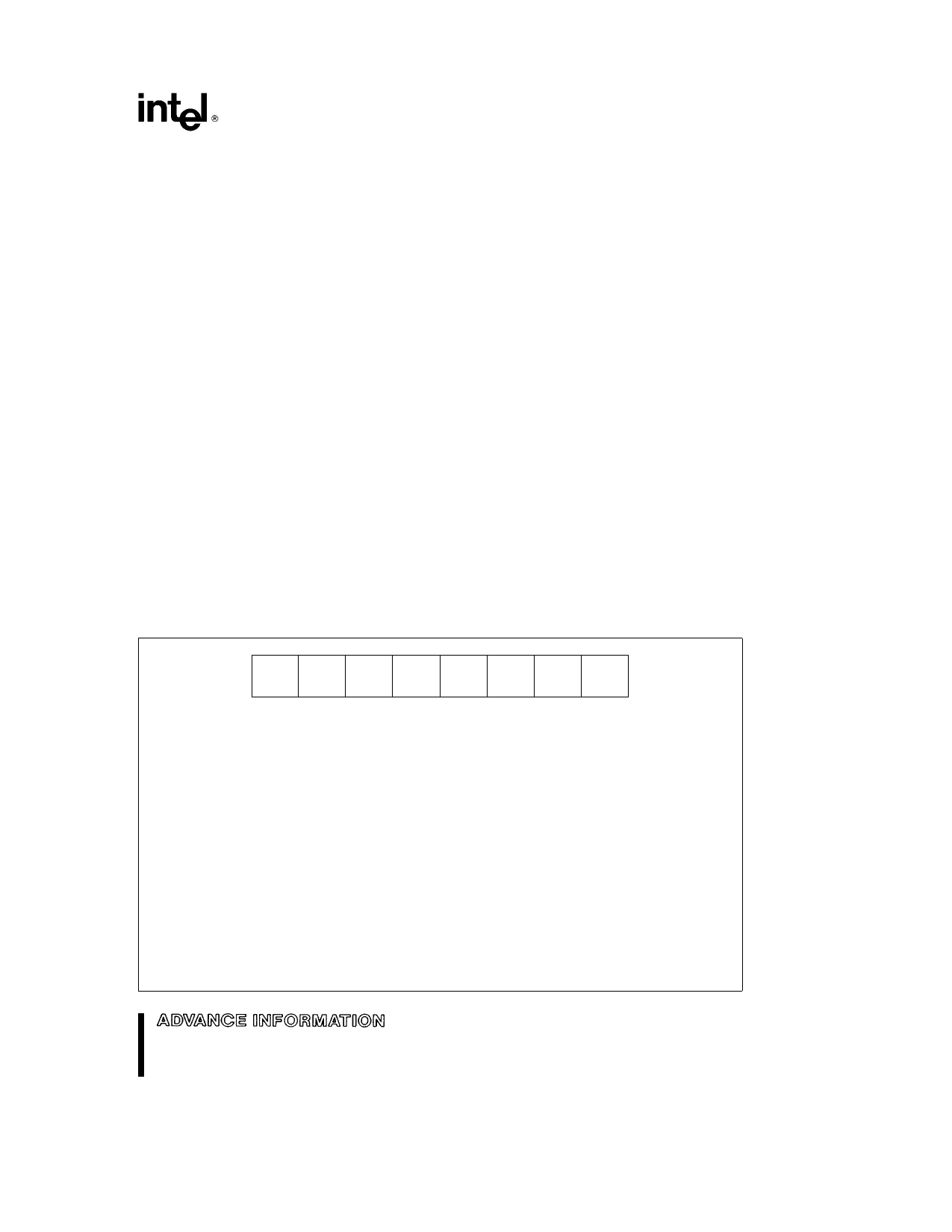

Table 4 Status Register Definitions

WSMS ESS ES BWS VPPS R R R

7654

SR 7 e WRITE STATE MACHINE STATUS

1 e Ready

0 e Busy

SR 6 e ERASE SUSPEND STATUS

1 e Erase Suspended

0 e Erase in Progress Completed

SR 5 e ERASE STATUS

1 e Error in Block Erasure

0 e Successful Block Erase

SR 4 e BYTE WRITE STATUS

1 e Error in Byte Write

0 e Successful Byte Write

SR 3 e VPP STATUS

1 e VPP Low Detect Operation Abort

0 e VPP OK

SR 2–SR 0 e RESERVED FOR FUTURE

ENHANCEMENTS

These bits are reserved for future use and

should be masked out when polling the Status

Register

3210

NOTES

RY BY or the Write State Machine Status bit must first

be checked to determine byte write or block erase com-

pletion before the Byte Write or Erase Status bit are

checked for success

If the Byte Write AND Erase Status bits are set to ‘‘1’’s

during a block erase attempt an improper command se-

quence was entered Attempt the operation again

If VPP low status is detected the Status Register must be

cleared before another byte write or block erase opera-

tion is attempted

The VPP Status bit unlike an A D converter does not

provide continuous indication of VPP level The WSM in-

terrogates the VPP level only after the byte write or block

erase command sequences have been entered and in-

forms the system if VPP has not been switched on The

VPP Status bit is not guaranteed to report accurate feed-

back between VPPL and VPPH

11

11 Page | ||

| Páginas | Total 28 Páginas | |

| PDF Descargar | [ Datasheet 28F008SA-L.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| 28F008SA-L | 8-MBIT (1 MBIT x 8) FLASHFILETM MEMORY | Intel |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |