No Preview Available !

19-0155; Rev 2; 1/96

Quad, Serial 8-Bit DACs

with Rail-to-Rail Outputs

_______________General Description

The MAX509/MAX510 are quad, serial-input, 8-bit volt-

age-output digital-to-analog converters (DACs). They

operate with a single +5V supply or dual ±5V supplies.

Internal, precision buffers swing rail-to-rail. The refer-

ence input range includes both supply rails.

The MAX509 has four separate reference inputs, allow-

ing each DAC's full-scale range to be set independently.

20-pin DIP, SSOP, and SO packages are available. The

MAX510 is identical to the MAX509 except it has two ref-

erence inputs, each shared by two DACs. The MAX510

is housed in space-saving 16-pin DIP and SO packages.

The serial interface is double-buffered: A 12-bit input

shift register is followed by four 8-bit buffer registers and

four 8-bit DAC registers. A 12-bit serial word is used to

load data into each register. Both input and DAC regis-

ters can be updated independently or simultaneously

with single software commands. Two additional asyn-

chronous control pins provide simultaneous updating

(LDAC) or clearing (CLR) of input and DAC registers.

The interface is compatible with MicrowireTM and SPI/

QSPITM. All digital inputs and outputs are TTL/CMOS

compatible. A buffered data output provides for read-

back or daisy-chaining of serial devices.

_______________Functional Diagrams

CLR

DOUT LDAC AGND DGND VSS VDD REFB REFA

DECODE

CONTROL

MAX509

INPUT

REG A

DAC

REG A

DAC A

OUTA

12-BIT

SHIFT

REGISTER

INPUT

REG B

DAC

REG B

DAC B

INPUT

REG C

DAC

REG C

DAC C

OUTB

OUTC

SR

CONTROL

INPUT

REG D

DAC

REG D

DAC D

OUTD

____________________________Features

o Single +5V or Dual ±5V Supply Operation

o Output Buffer Amplifiers Swing Rail-to-Rail

o Reference Input Range Includes Both Supply Rails

o Calibrated Offset, Gain, and Linearity (1LSB TUE)

o 10MHz Serial Interface, Compatible with SPI, QSPI

(CPOL = CPHA = 0) and Microwire

o Double-Buffered Registers for Synchronous

Updating

o Serial Data Output for Daisy-Chaining

o Power-On Reset Clears Serial Interface and Sets

All Registers to Zero

______________Ordering Information

PART

MAX509ACPP

MAX509BCPP

MAX509ACWP

MAX509BCWP

MAX509ACAP

MAX509BCAP

MAX509BC/D

TEMP. RANGE

0°C to +70°C

0°C to +70°C

0°C to +70°C

0°C to +70°C

0°C to +70°C

0°C to +70°C

0°C to +70°C

PIN-PACKAGE

20 Plastic DIP

20 Plastic DIP

20 Wide SO

20 Wide SO

20 SSOP

20 SSOP

Dice*

TUE

(LSB)

±1

±1 1/2

±1

±1 1/2

±1

±1 1/2

±1 1/2

Ordering Information continued on last page.

* Dice are specified at +25°C, DC parameters only.

**Contact factory for availability and processing to MIL-STD-883.

_________________Pin Configurations

TOP VIEW

OUTB 1

OUTA 2

VSS 3

REFB 4

REFA 5

AGND 6

N.C. 7

DGND 8

LDAC 9

DOUT 10

MAX509

20 OUTC

19 OUTD

18 VDD

17 REFC

16 REFD

15 CS

14 N.C.

13 SCLK

12 DIN

11 CLR

CS DIN SCLK

REFC REFD

Functional Diagrams continued at end of data sheet.

DIP/SO/SSOP

Pin Configurations continued at end of data sheet.

Microwire is a trademark of National Semiconductor. SPI and QSPI are trademarks of Motorola.

________________________________________________________________ Maxim Integrated Products 1

For free samples & the latest literature: http://www.maxim-ic.com, or phone 1-800-998-8800

Quad, Serial 8-Bit DACs

with Rail-to-Rail Outputs

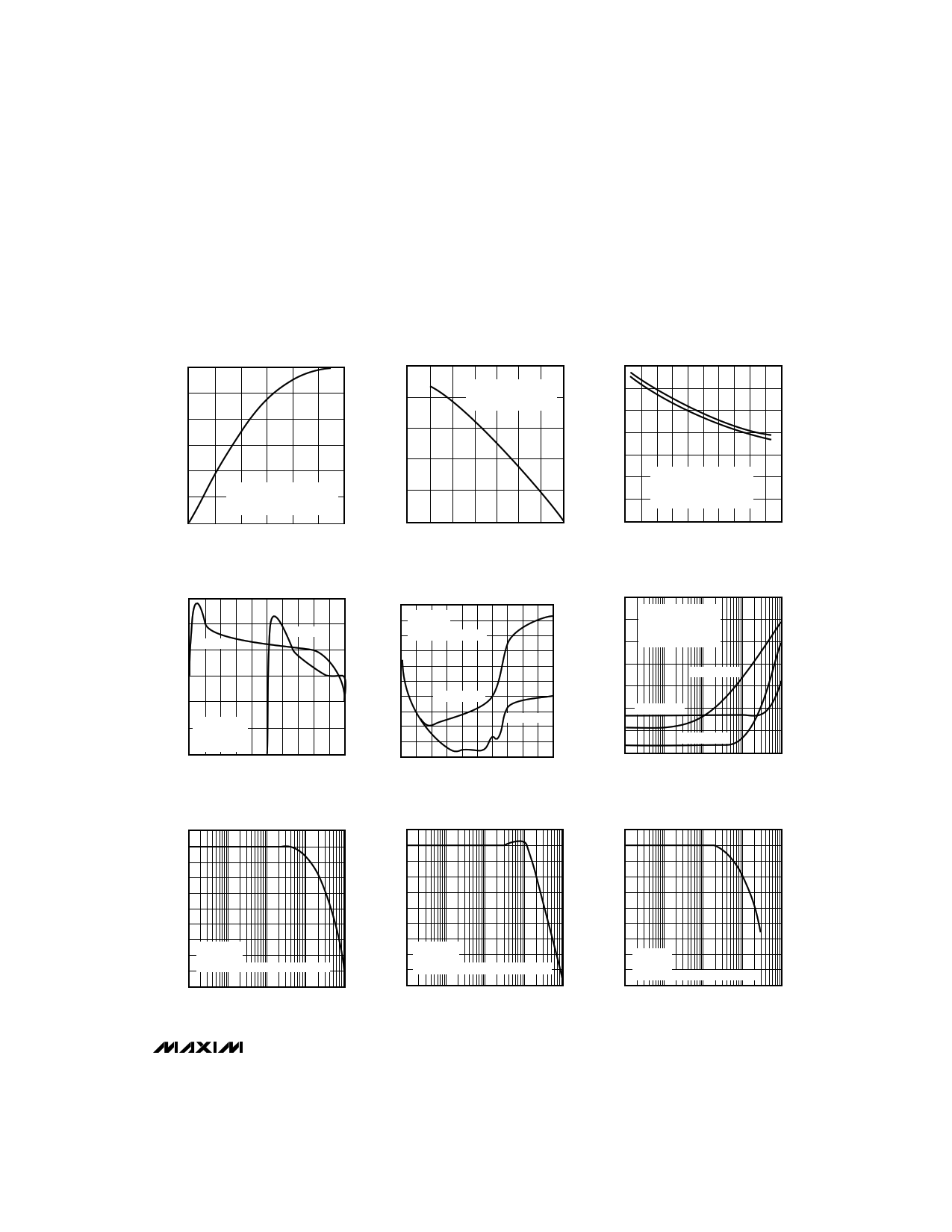

__________________________________________Typical Operating Characteristics

(TA = +25°C, unless otherwise noted.)

OUTPUT SINK CURRENT

vs. (VOUT - VSS)

12

10

8

6

4

2

0

0

VDD = VREF = +5V

VSS = GND = 0V

ALL DIGITAL INPUTS = 00 HEX

0.2 0.4 0.6 0.8 1.0 1.2

VOUT - VSS (V)

SUPPLY CURRENT

vs. REFERENCE VOLTAGE

6

5

4 VSS = -5V

VSS = 0V

3

2

1

VDD = +5V

ALL LOGIC

INPUTS = +5V

0

-5 -4 -3 -2 -1 0 1 2 3 4 5

VREF VOLTAGE (V)

REFERENCE VOLTAGE INPUT

FREQUENCY RESPONSE

0

-10

OUTPUT SOURCE CURRENT

vs. OUTPUT VOLTAGE

-25

VDD = VREF = +5V

-20 VSS = GND

DIGITAL INPUT = FF HEX

-15

-10

-5

0

3.6 3.8 4.0 4.2 4.4 4.6 4.8 5.0

VOUT (V)

THD + NOISE AT DAC OUTPUT

vs. REFERENCE AMPLITUDE

-40

-45

VDD = +5V

VSS = -5V

-50 INPUT CODE = FF HEX

1%

-55

-60 0.1%

-65

-70 FREQ = 20kHz

-75

FREQ = 1kHz

-80 0.01%

-85

-90

0

24 6 8

REFERENCE AMPLITUDE (Vp-p)

10

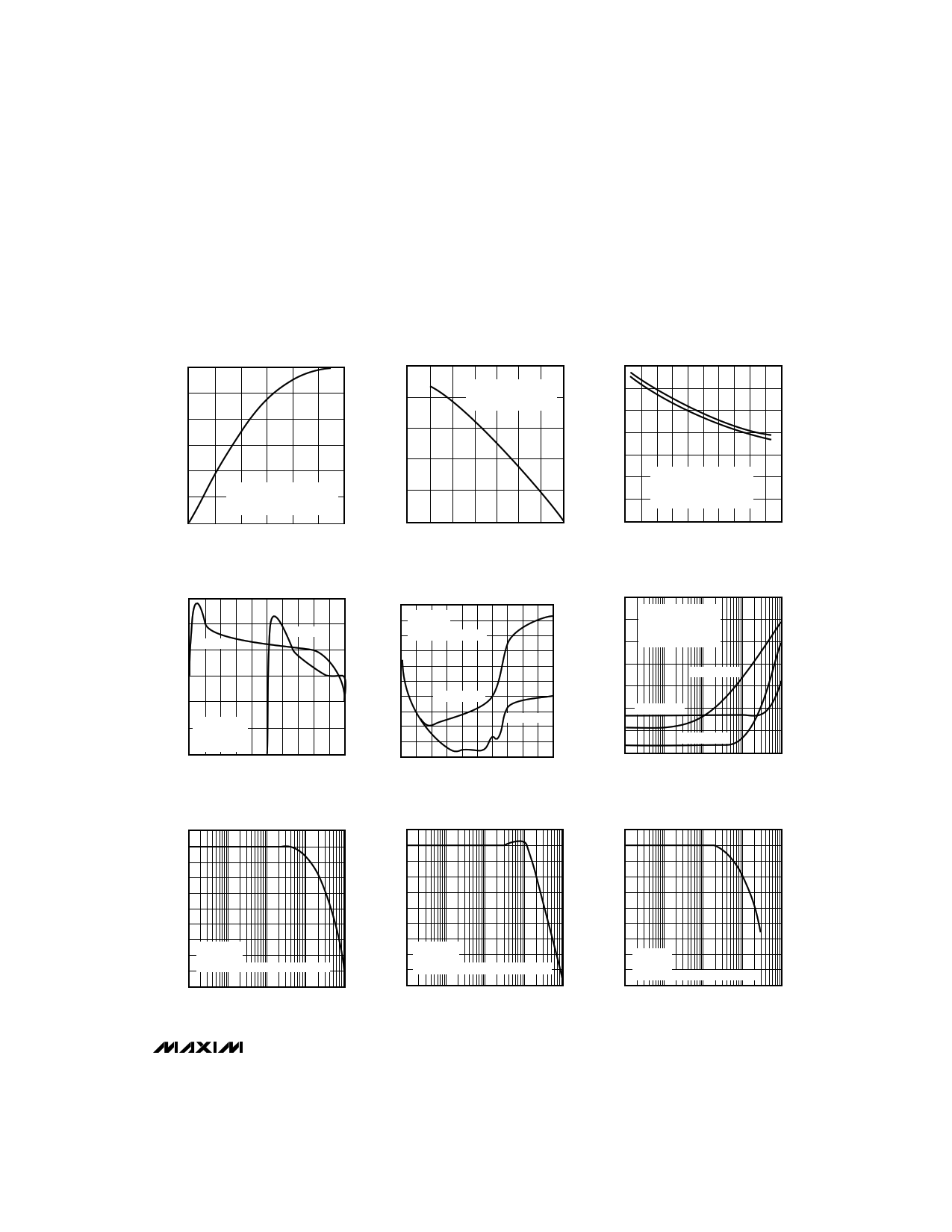

REFERENCE VOLTAGE INPUT

FREQUENCY RESPONSE

0

SUPPLY CURRENT

vs. TEMPERATURE

7

6

5

IDD

4

ISS

3

2

VDD = +5.5V

VSS = -5.5V

VREF = -4.75

1 ALL DIGITAL INPUTS = +5V

0

-60 -40 -20 0 20 40 60 80 100 120 140

TEMPERATURE (°C)

THD + NOISE AT DAC OUTPUT

vs. REFERENCE FREQUENCY

-20 10%

-30

VDD = +5V

VSS = -5V

INPUT CODE = FF HEX

-40 FREQ = SWEPT

1%

-50

VREF = 8Vp-p

-60 0.1%

-70 VREF = 1Vp-p

-80

-90

10

VREF = 4Vp-p

0.01%

100 1k 10k

REFERENCE FREQUENCY (Hz)

100k

REFERENCE VOLTAGE INPUT

FREQUENCY RESPONSE

0

-10 -10

-20

-30

VDD = +5V

VSS = AGND

-40 VREF = 2.5VDC + 0.5Vp-p SINE WAVE

1k 10k 100k 1M 10M

FREQUENCY (Hz)

-20

-30

VDD = +5V

VSS = AGND

-40 VREF = 2.5VDC + 0.05Vp-p SINE WAVE

1k 10k 100k 1M 10M

FREQUENCY (Hz)

-20

-30

VDD = +5V

-40

VSS = -5V

VREF = 2.5VDC + 4Vp-p SINE WAVE

1k 10k 100k 1M 10M

FREQUENCY (Hz)

_______________________________________________________________________________________ 5

Quad, Serial 8-Bit DACs

with Rail-to-Rail Outputs

Serial Input Data Format and Control Codes

The 12-bit serial input format shown in Figure 3 com-

prises two DAC address bits (A1, A0), two control bits

(C1, C0) and eight bits of data (D0...D7).

The 4-bit address/control code configures the DAC as

shown in Table 1.

DOUT

This is the first bit shifted in

MSB

LSB

A1 A0C1 C0 D7D6

q q q D1 D0

DIN

Control and

Address bits

Figure 3. Serial Input Format

8-bit DAC data

Load Input Register, DAC Registers Unchanged

(Single Update Operation)

A1 A0 C1 C0 D7 D6 D5 D4 D3 D2 D1 D0

Address 0 1

8-Bit Data

(LDAC = H)

When performing a single update operation, A1 and A0

select the respective input register. At the rising edge

of CS, the selected input register is loaded with the cur-

rent shift-register data. All DAC outputs remain

unchanged. This preloads individual data in the input

register without changing the DAC outputs.

Load Input and DAC Registers

A1 A0 C1 C0 D7 D6 D5 D4 D3 D2 D1 D0

Address 1 1

8-Bit Data

(LDAC = H)

This command directly loads the selected DAC register

at CS's rising edge. A1 and A0 set the DAC address.

Current shift-register data is placed in the selected

input and DAC registers.

For example, to load all four DAC registers simultaneously

with individual settings (DAC A = 1V, DAC B = 2V, DAC

C = 3V and DAC D = 4V), five commands are required.

First, perform four single input register update opera-

tions. Next, perform an “LDAC” command as a fifth

command. All DACs will be updated from their respec-

tive input registers at the rising edge of CS.

Update All DACs from Shift Registers

A1 A0 C1 C0 D7 D6 D5 D4 D3 D2 D1 D0

x 00 0

8-Bit DAC Data

(LDAC = x)

All four DAC registers are updated with shift-register

data. This command allows all DACs to be set to any

analog value within the reference range. This command

can be used to substitute CLR if code 00 hex is pro-

grammed, which clears all DACs.

No Operation (NOP)

A1 A0 C1 C0 D7 D6 D5 D4 D3 D2 D1 D0

x 1 0 0 xxx xx xxx

(LDAC = x)

The NOP command (no operation) allows data to be shift-

ed through the MAX509/MAX510 shift register without

affecting the input or DAC registers. This is useful in daisy

chaining (also see the Daisy-Chaining Devices section).

For this command, the data bits are "Don't Cares." As an

example, three MAX509/MAX510s are daisy-chained (A, B

and C), and DAC A and DAC C need to be updated. The

36-bit-wide command would consist of one 12-bit word for

device C, followed by an NOP instruction for device B and

a third 12-bit word with data for device A. At CS's rising

edge, only device B is not updated.

“LDAC” Command (Software)

A1 A0 C1 C0 D7 D6 D5 D4 D3 D2 D1 D0

0 x 1 0 xx x xx x xx

(LDAC = x)

All DAC registers are updated with the contents of their

respective input registers at CS's rising edge. With the

exception of using CS to execute, this performs the

same function as the asynchronous LDAC.

Set DOUT Phase – SCLK Rising (Mode 1, Default)

A1 A0 C1 C0 D7 D6 D5 D4 D3 D2 D1 D0

1 11 0 xx x xx x xx

(LDAC = x)

Mode 1 resets the serial output DOUT to transition at

SCLK's rising edge. This is the MAX509/MAX510’s

default setting after the supply voltage has been

applied.

The command also loads all DAC registers with the con-

tents of their respective input registers, and is identical to

the “LDAC” command.

______________________________________________________________________________________ 11