|

|

PDF 74LS374 Data sheet ( Hoja de datos )

| Número de pieza | 74LS374 | |

| Descripción | 3-STATE Octal D-Type Transparent Latches and Edge-Triggered Flip-Flops | |

| Fabricantes | Fairchild Semiconductor | |

| Logotipo | ||

Hay una vista previa y un enlace de descarga de 74LS374 (archivo pdf) en la parte inferior de esta página. Total 8 Páginas | ||

|

No Preview Available !

April 1986

Revised March 2000

DM74LS373 • DM74LS374

3-STATE Octal D-Type Transparent Latches

and Edge-Triggered Flip-Flops

General Description

These 8-bit registers feature totem-pole 3-STATE outputs

designed specifically for driving highly-capacitive or rela-

tively low-impedance loads. The high-impedance state and

increased high-logic level drive provide these registers with

the capability of being connected directly to and driving the

bus lines in a bus-organized system without need for inter-

face or pull-up components. They are particularly attractive

for implementing buffer registers, I/O ports, bidirectional

bus drivers, and working registers.

The eight latches of the DM74LS373 are transparent D-

type latches meaning that while the enable (G) is HIGH the

Q outputs will follow the data (D) inputs. When the enable

is taken LOW the output will be latched at the level of the

data that was set up.

The eight flip-flops of the DM74LS374 are edge-triggered

D-type flip flops. On the positive transition of the clock, the

Q outputs will be set to the logic states that were set up at

the D inputs.

A buffered output control input can be used to place the

eight outputs in either a normal logic state (HIGH or LOW

logic levels) or a high-impedance state. In the high-imped-

ance state the outputs neither load nor drive the bus lines

significantly.

The output control does not affect the internal operation of

the latches or flip-flops. That is, the old data can be

retained or new data can be entered even while the outputs

are OFF.

Features

s Choice of 8 latches or 8 D-type flip-flops in a single

package

s 3-STATE bus-driving outputs

s Full parallel-access for loading

s Buffered control inputs

s P-N-P inputs reduce D-C loading on data lines

Ordering Code:

Order Number Package Number

Package Description

DM74LS373WM

M20B

20-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-013, 0.300 Wide

DM74LS373SJ

M20D

20-Lead Small Outline Package (SOP), EIAJ TYPE II, 5.3mm Wide

DM74LS373N

N20A

20-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-001, 0.300 Wide

DM74LS374WM

M20B

20-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-013, 0.300 Wide

DM74LS374SJ

M20D

20-Lead Small Outline Package (SOP), EIAJ TYPE II, 5.3mm Wide

IDM29901NC

N20A

20-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-001, 0.300 Wide

Devices also available in Tape and Reel. Specify by appending the suffix letter “X” to the ordering code.

© 2000 Fairchild Semiconductor Corporation DS006431

www.fairchildsemi.com

1 page

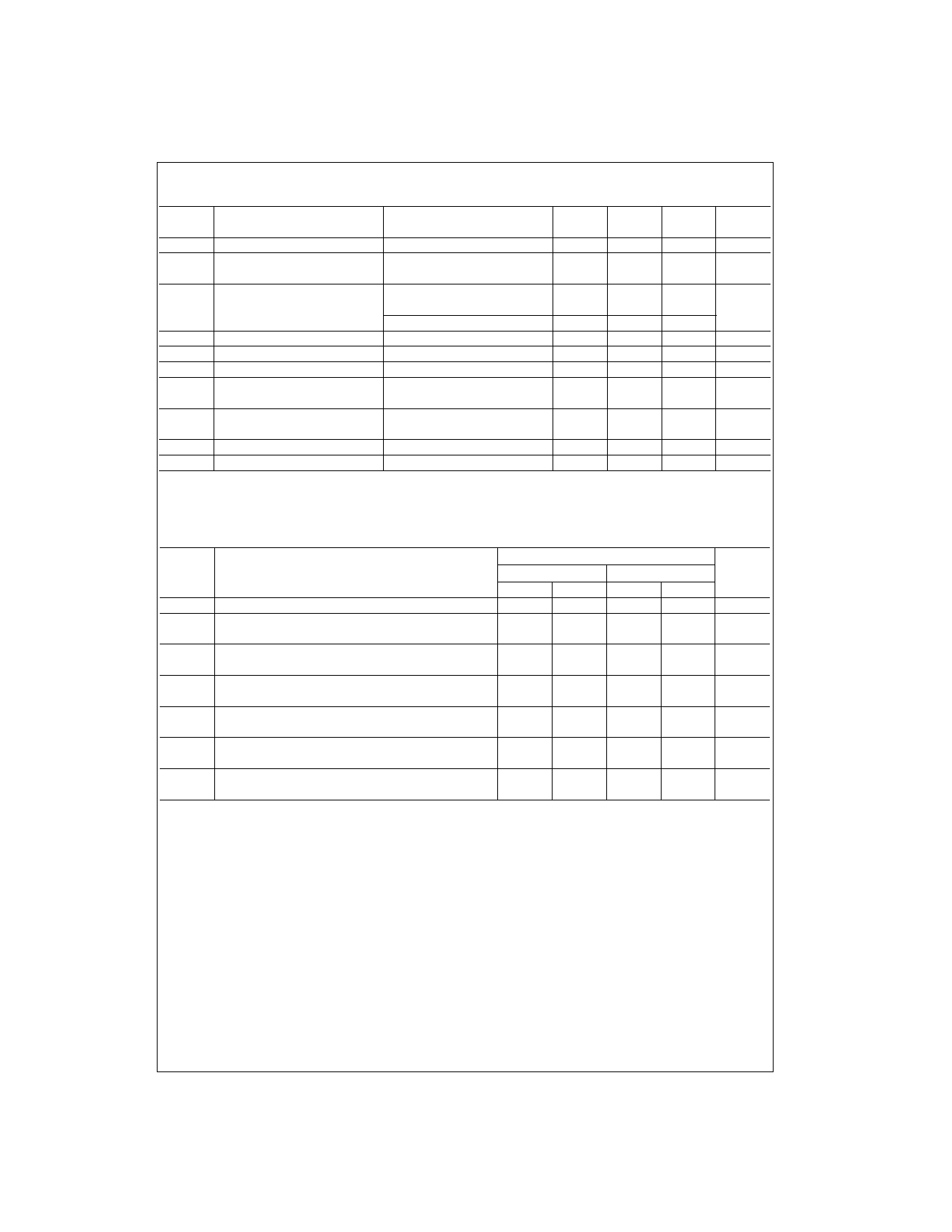

DM74LS374 Electrical Characteristics

over recommended operating free air temperature range (unless otherwise noted)

Symbol

Parameter

Conditions

Min

VI Input Clamp Voltage

VCC = Min, II = −18 mA

VOH HIGH Level

Output Voltage

VCC = Min, IOH = Max

VIL = Max, VIH = Min

2.4

VOL LOW Level

VCC = Min, IOL = Max

Output Voltage

VIL = Max, VIH = Min

IOL = 12 mA, VCC = Min

II

Input Current @ Max Input Voltage

VCC = Max, VI = 7V

IIH HIGH Level Input Current

VCC = Max, VI = 2.7V

IIL LOW Level Input Current

VCC = Max, VI = 0.4V

IOZH

Off-State Output Current with

VCC = Max, VO = 2.7V

HIGH Level Output Voltage Applied

VIH = Min, VIL = Max

IOZL Off-State Output Current with

VCC = Max, VO = 0.4V

LOW Level Output Voltage Applied

VIH = Min, VIL = Max

IOS Short Circuit Output Current

VCC = Max (Note 10)

−50

ICC Supply Current

VCC = Max, Dn = GND, OC = 4.5V

Note 9: All typicals are at VCC = 5V, TA = 25°C.

Note 10: Not more than one output should be shorted at a time, and the duration should not exceed one second.

Typ

(Note 9)

3.1

0.35

0.25

27

Max

−1.5

0.5

0.4

0.1

20

−0.4

20

−20

−225

45

DM74LS374 Switching Characteristics

at VCC = 5V and TA = 25°C

Symbol

Parameter

fMAX

tPLH

Maximum Clock Frequency

Propagation Delay Time

LOW-to-HIGH Level Output

tPHL Propagation Delay Time

HIGH-to-LOW Level Output

tPZH Output Enable Time

to HIGH Level Output

tPZL Output Enable Time

to LOW Level Output

tPHZ Output Disable Time

from HIGH Level Output (Note 11)

tPLZ Output Disable Time

from LOW Level Output (Note 11)

Note 11: CL = 5 pF.

RL = 667Ω

CL = 45 pF

CL = 150 pF

Min Max Min Max

35 20

28 32

28 38

28 44

28 44

20

25

Units

V

V

V

mA

µA

mA

µA

µA

mA

mA

Units

MHz

ns

ns

ns

ns

ns

ns

5 www.fairchildsemi.com

5 Page | ||

| Páginas | Total 8 Páginas | |

| PDF Descargar | [ Datasheet 74LS374.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| 74LS37 | Quadruple 2-input Positive NAND Buffers | Hitachi Semiconductor |

| 74LS37 | 3-STATE Octal D-Type Transparent Latches and Edge-Triggered Flip-Flops | Fairchild Semiconductor |

| 74LS37 | TRI-STATEE Octal D-Type Transparent Latches and Edge-Triggered Flip-Flops | National Semiconductor |

| 74LS373 | TRI-STATEE Octal D-Type Transparent Latches and Edge-Triggered Flip-Flops | National Semiconductor |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |