|

|

PDF EM565161BA-55E Data sheet ( Hoja de datos )

| Número de pieza | EM565161BA-55E | |

| Descripción | 512K x 16 Low Power SRAM | |

| Fabricantes | Etron Technology Inc. | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de EM565161BA-55E (archivo pdf) en la parte inferior de esta página. Total 13 Páginas | ||

|

No Preview Available !

Et r onT ec h

EM565161

512K x 16 Low Power SRAM

Preliminary, Rev 0.9 01/2002

Features

• Single Power Supply Voltage, 2.3 ~ 3.6 V

• Power Down Features Using CE1#, CE2, LB# and

UB#

• Low Power Dissipation

• Data retention Supply Voltage: 1.0V to 3.6V

• Direct TTL Compatibility for All Input and Output

• Wide Operating Temperature Range: -40°C to 85°C

• Standby current (maximum) @ VDD = 3.6 V

Part Number

IDDS2

Typical Maximum

EM565161BA/BJ-55

2 µA

35 µA

EM565161BA/BJ-70

2 µA

25 µA

EM565161BA/BJ-55E/70E 14 µA

80 µA

Ordering Information

Part Number

Speed

EM565161BJ-70 70 ns

EM565161BA-70 70 ns

EM565161BA-70E 70 ns

EM565161BJ-55 55 ns

EM565161BA-55 55 ns

EM565161BA-55E 55 ns

IDDS2

25 µA

25 µA

80 µA

35 µA

35 µA

80 µA

Package

6x9 BGA

8x10 BGA

8x10 BGA

6x9 BGA

8x10 BGA

8x10 BGA

Pin Assignment

48-Ball BGA (CSP), Top View

12345

6

A

LB# OE#

A0

A1

A2 CE2

B

DQ8 UB#

A3

A4 CE1# DQ0

C

DQ9 DQ10 A5

A6 DQ1 DQ2

D

GND DQ11 A17

A7

DQ3 VDD

E

VDD DQ12 GND

A16

DQ4 GND

F

DQ14 DQ13 A14

A15

DQ5 DQ6

G

DQ15 NC

A12

A13 W E# DQ7

H

A18

A8

A9 A10 A11 NC

Pin Names

Symbol

A0 – A18

DQ0-DQ15

CE1#,CE2

OE#

WE#

LB#,UB#

GND

VDD

NC

Function

Address Inputs

Data Inputs/Outputs

Chip Enable Input

Output Enable

Read/Write Control Input

Data Byte Control Inputs

Ground

Power Supply

No Connection

Overview

The EM565161 is an 8M-bit SRAM organized as 512K words by 16 bits. It is designed with advanced CMOS

technology. This Device operates from a single power supply. Advanced circuit technology provides both high

speed and low power. It is automatically placed in low-power mode when CE1# or both UB# and LB# are

asserted high or CE2 is asserted low. There are three control inputs. CE1# and CE2 are used to select the

device and for data retention control, and output enable (OE#) provides fast memory access. Data byte control

pin (LB#,UB#) provides lower and upper byte access. This device is well suited to various microprocessor

system applications where high speed, low power and battery backup are required. And, with a guaranteed

operating range from –40°C to 85°C, the EM565161 can be used in environments exhibiting extreme

temperature conditions.

Etron Technology, Inc.

No. 6, Technology Rd. V, Science-Based Industrial Park, Hsinchu, Taiwan 30077, R.O.C.

TEL: (886)-3-5782345 FAX: (886)-3-5778671

Etron Technology, Inc., reserves the right to make changes to its products and specifications without notice.

1 page

Et r onT ec h

EM565161

AC Characteristics and Operating Conditions (Ta = -40°C to 85°C, VDD = 2.3V to 3.6V)

Read Cycle

EM565161

Symbol

Parameter

-55 -70 Unit

Min Max Min Max

tRC

tAA

tCO1

tCO2

tOE

tBA

tLZ

tOLZ

tBLZ

tHZ

tOHZ

tBHZ

tOH

Write Cycle

Read cycle time

Address access time

Chip Enable (CE1#) Access Time

Chip Enable (CE2) Access Time

Output enable access time

Data Byte Control Access Time

Chip Enable Low to Output in Low-Z

Output enable Low to Output in Low-Z

Data Byte Control Low to Output in Low-Z

Chip Enable High to Output in High-Z

Output Enable High to Output in High-Z

Data Byte Control High to Output in High-Z

Output Data Hold Time

Symbol

Parameter

55 − 70 −

− 55 − 70

− 55 − 70

− 55 − 70

− 25 − 35

− 55 − 70

10 − 10 −

5−5−

10 − 10 −

− 20 − 25

− 20 − 25

− 20 − 25

10 − 10 −

ns

EM565161

-55 -70

Min Max Min Max

Unit

tWC

tWP

tCW

tBW

tAS

tWR

tWHZ

tOW

tDS

tDH

Write cycle time

Write pulse width

Chip Enable to end of write

Data Byte Control to end of Write

Address setup time

Write Recovery time

WE# Low to Output in High-Z

WE# High to Output in Low-Z

Data Setup Time

Data Hold Time

55 − 70 −

45 − 55 −

45 − 60 −

45 − 60 −

0−0−

0−0−

− 20 − 20

5−5−

25 − 30 −

0−0−

ns

AC Test Condition

• Output load : 60pF + one TTL gate

• Input pulse level : 0.4V, 2.4V

• Timing measurements : 0.5 x VDD

• tR, tF : 5ns

Preliminary

5

Rev 0.9

Jan 2002

5 Page

Et r onT ec h

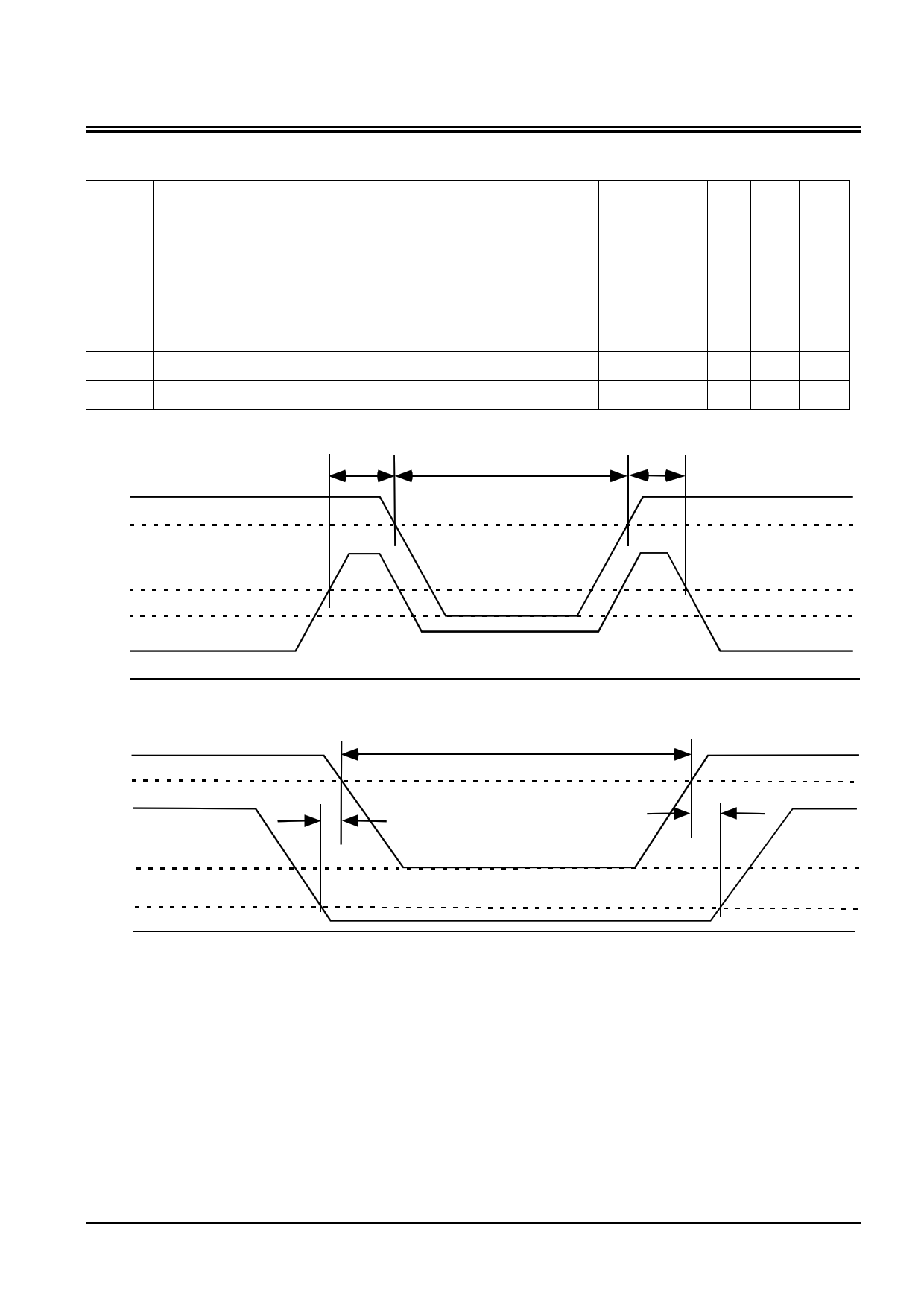

Data Retention Characteristics (Ta = -40°C to 85°C)

Symbol

Parameter

CE1# ≥ VDD – 0.2V

VDR

Data Retention Supply

Voltage

or UB# = LB# ≥ VDD – 0.2V

or CE2 ≤ 0.2V,

VIN ≥ VDD – 0.2V or VIN ≤ 0.2V

tSDR Chip Deselect to Data Retention Mode Time

tRDR Recovery Time

CE1# or UB#/LB# Controlled Data Retention Mode

tS D R

Data Retention Mode

VDD

2 .7 V

2 .2 V

VDR

CE1#,

U B # /L B #

GND

Note 1

CE2 Controlled Data Retention Mode

VDD

2.7V

CE2

tSDR

Data Retention Mode

VDR

0.4V

GND

Note 2

Note:

1. CE1# ≥ VDD – 0.2V or UB# = LB# ≥ VDD – 0.2V

2. CE2 ≤ 0.2V

EM565161

Min Typ Max Unit

1.0 − 3.6 V

0

tRC

tR D R

− − ns

− − ns

tRDR

Preliminary

11

Rev 0.9

Jan 2002

11 Page | ||

| Páginas | Total 13 Páginas | |

| PDF Descargar | [ Datasheet EM565161BA-55E.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| EM565161BA-55 | 512K x 16 Low Power SRAM | Etron Technology Inc. |

| EM565161BA-55E | 512K x 16 Low Power SRAM | Etron Technology Inc. |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |