|

|

PDF ATmega323 Data sheet ( Hoja de datos )

| Número de pieza | ATmega323 | |

| Descripción | 8-bit Microcontroller with 32K Bytes of In-System Programmable Flash | |

| Fabricantes | ATMEL Corporation | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de ATmega323 (archivo pdf) en la parte inferior de esta página. Total 70 Páginas | ||

|

No Preview Available !

Features

• High-performance, Low-power AVR® 8-bit Microcontroller

• Advanced RISC Architecture

– 130 Powerful Instructions – Most Single-clock Cycle Execution

– 32 x 8 General Purpose Working Registers

– Fully Static Operation

– Up to 8 MIPS Throughput at 8 MHz

– On-chip 2-cycle Multiplier

• Non-volatile Program and Data Memories

– 32K Bytes of In-System Self-programmable Flash

Endurance: 1,000 Write/Erase Cycles

– Optional Boot Code Section with Independent Lock Bits

In-System Programming by On-chip Boot Program

– 1K Byte EEPROM

Endurance: 100,000 Write/Erase Cycles

– 2K Bytes Internal SRAM

– Programming Lock for Software Security

• JTAG (IEEE Std. 1149.1 Compliant) Interface

– Extensive On-chip Debug Support

– Programming of Flash, EEPROM, Fuses, and Lock Bits through the JTAG Interface

– Boundary-Scan Capabilities According to the JTAG Standard

• Peripheral Features

– Two 8-bit Timer/Counters with Separate Prescaler and Compare Mode

– One 16-bit Timer/Counter with Separate Prescaler, Compare Mode, and Capture

Mode

– Real Time Counter with Separate Oscillator

– Four PWM Channels

– 8-channel, 10-bit ADC

– Byte-oriented Two-wire Serial Interface

– Programmable Serial USART

– Master/Slave SPI Serial Interface

– Programmable Watchdog Timer with Separate On-chip Oscillator

– On-chip Analog Comparator

• Special Microcontroller Features

– Power-on Reset and Programmable Brown-out Detection

– Internal Calibrated RC Oscillator

– External and Internal Interrupt Sources

– Six Sleep Modes: Idle, ADC Noise Reduction, Power-save, Power-down, Standby

and Extended Standby

• I/O and Packages

– 32 Programmable I/O Lines

– 40-pin PDIP and 44-lead TQFP

• Operating Voltages

– 2.7 - 5.5V (ATmega323L)

– 4.0 - 5.5V (ATmega323)

• Speed Grades

– 0 - 4 MHz (ATmega323L)

– 0 - 8 MHz (ATmega323)

8-bit

Microcontroller

with 32K Bytes

of In-System

Programmable

Flash

ATmega323

ATmega323L

Not recommended

for new designs.

Use ATmega32.

1457G–AVR–09/03

1 page

Port B (PB7..PB0)

Port C (PC7..PC0)

Port D (PD7..PD0)

RESET

XTAL1

XTAL2

AVCC

AREF

AGND

ATmega323(L)

Port B is an 8-bit bi-directional I/O port with internal pull-up resistors (selected for each

bit). The Port B output buffers can sink 20 mA. As inputs, Port B pins that are externally

pulled low will source current if the pull-up resistors are activated. The Port B pins are

tri-stated when a reset condition becomes active, even if the clock is not running.

Port B also serves the functions of various special features of the ATmega323 as listed

on page 139.

Port C is an 8-bit bi-directional I/O port with internal pull-up resistors (selected for each

bit). The Port C output buffers can sink 20 mA. As inputs, Port C pins that are externally

pulled low will source current if the pull-up resistors are activated. The Port C pins are

tri-stated when a reset condition becomes active, even if the clock is not running.

Port C also serves the functions of the JTAG interface and other special features of the

ATmega323 as listed on page 146. If the JTAG interface is enabled, the pull-up resistors

on pins PC5 (TDI), PC3 (TMS) and PC2 (TCK) will be activated even if a Reset occurs.

Port D is an 8-bit bidirectional I/O port with internal pull-up resistors (selected for each

bit). The Port D output buffers can sink 20 mA. As inputs, Port D pins that are externally

pulled low will source current if the pull-up resistors are activated. The Port D pins are

tri-stated when a reset condition becomes active, even if the clock is not running.

Port D also serves the functions of various special features of the ATmega323 as listed

on page 151.

Reset input. A low level on this pin for more than 500 ns will generate a Reset, even if

the clock is not running. Shorter pulses are not guaranteed to generate a Reset.

Input to the inverting Oscillator amplifier and input to the internal clock operating circuit.

Output from the inverting Oscillator amplifier.

AVCC is the supply voltage pin for Port A and the A/D Converter. It should be externally

connected to VCC, even if the ADC is not used. If the ADC is used, it should be con-

nected to VCC through a low-pass filter. See page 127 for details on operation of the

ADC.

AREF is the analog reference pin for the A/D Converter. For ADC operations, a voltage

in the range 2.56V to AVCC can be applied to this pin.

Analog ground. If the board has a separate analog ground plane, this pin should be con-

nected to this ground plane. Otherwise, connect to GND.

1457G–AVR–09/03

5

5 Page

ATmega323(L)

The General Purpose

Register File

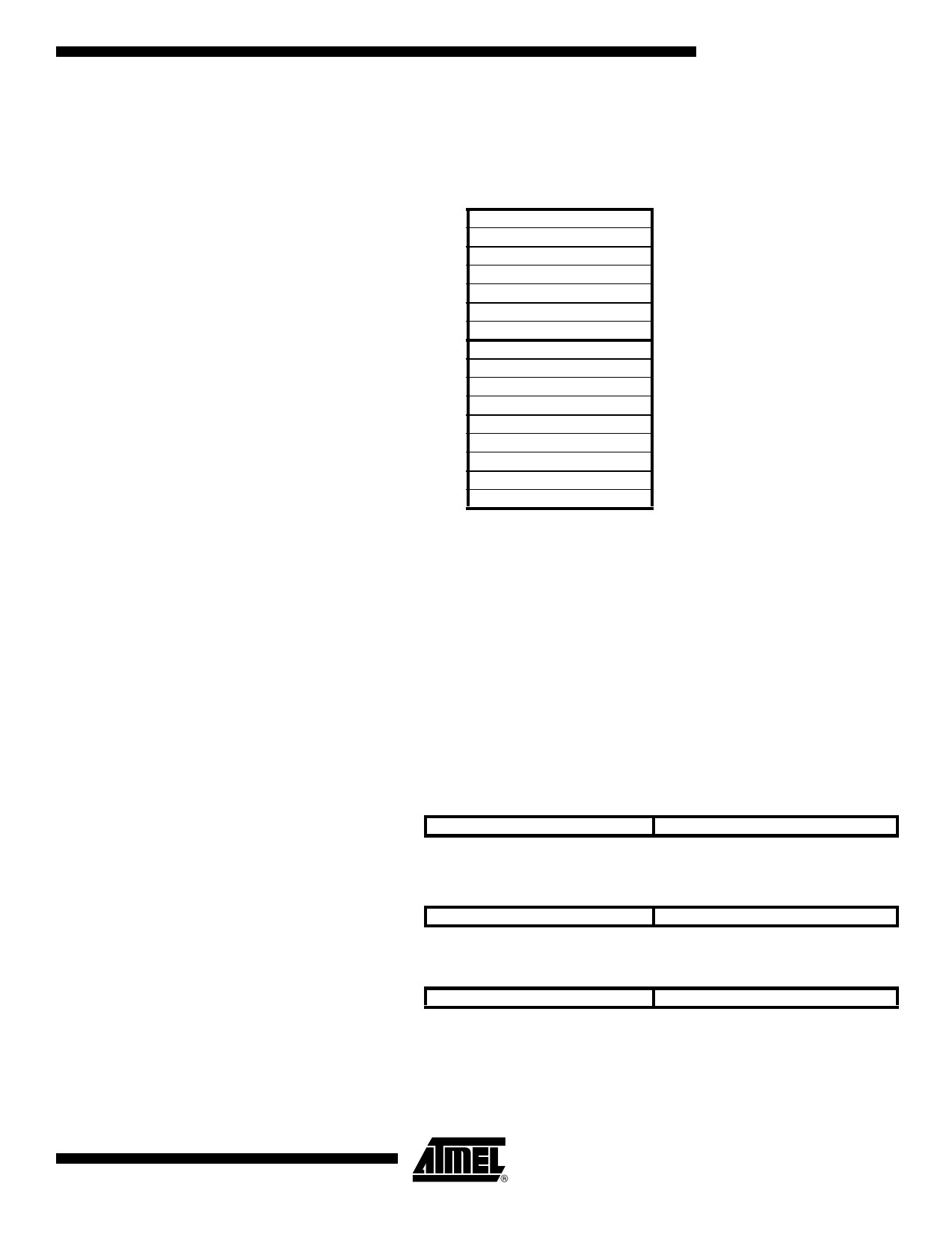

Figure 7 shows the structure of the 32 general purpose working registers in the CPU.

Figure 7. AVR CPU General Purpose Working Registers

General

Purpose

Working

Registers

70

R0

R1

R2

…

R13

R14

R15

R16

R17

…

R26

R27

R28

R29

R30

R31

Addr.

$00

$01

$02

$0D

$0E

$0F

$10

$11

$1A

$1B

$1C

$1D

$1E

$1F

X-register Low Byte

X-register High Byte

Y-register Low Byte

Y-register High Byte

Z-register Low Byte

Z-register High Byte

Most register operating instructions in the instruction set have direct access to all regis-

ters, and most of them are single cycle instructions.

As shown in Figure 7, each register is also assigned a Data memory address, mapping

them directly into the first 32 locations of the user Data Space. Although not being phys-

ically implemented as SRAM locations, this memory organization provides great

flexibility in access of the registers, as the X-, Y-, and Z-registers can be set to index any

register in the file.

The X-register, Y-register, and The registers R26..R31 have some added functions to their general purpose usage.

Z-register

These registers are address pointers for indirect addressing of the Data Space. The

three indirect address registers X, Y, and Z are defined as:

Figure 8. The X-, Y-, and Z-registers

X - register

15

70

R27 ($1B)

XH

XL

07

R26 ($1A)

0

0

Y - register

15

70

R29 ($1D)

YH

YL

07

R28 ($1C)

0

0

Z - register

15

70

R31 ($1F)

ZH

ZL

07

R30 ($1E)

0

0

In the different addressing modes these address registers have functions as fixed dis-

placement, automatic increment and decrement (see the descriptions for the different

instructions).

1457G–AVR–09/03

11

11 Page | ||

| Páginas | Total 70 Páginas | |

| PDF Descargar | [ Datasheet ATmega323.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| ATMEGA32 | 8-bit AVR Microcontroller with 32K Bytes In-System Programmable Flash | ATMEL Corporation |

| ATmega323 | 8-bit Microcontroller with 32K Bytes of In-System Programmable Flash | ATMEL Corporation |

| ATMEGA323L | 8-bit Microcontroller with 32K Bytes of In-System Programmable Flash | ATMEL Corporation |

| ATMEGA324 | (ATMEGAxx4) 8-bit Microcontroller | ATMEL Corporation |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |