|

|

PDF AM28F010A-120EC Data sheet ( Hoja de datos )

| Número de pieza | AM28F010A-120EC | |

| Descripción | 1 Megabit (128 K x 8-Bit) CMOS 12.0 Volt/ Bulk Erase Flash Memory with Embedded Algorithms | |

| Fabricantes | Advanced Micro Devices | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de AM28F010A-120EC (archivo pdf) en la parte inferior de esta página. Total 35 Páginas | ||

|

No Preview Available !

FINAL

Am28F010A

1 Megabit (128 K x 8-Bit)

CMOS 12.0 Volt, Bulk Erase Flash Memory with Embedded Algorithms

DISTINCTIVE CHARACTERISTICS

s High performance

— Access times as fast as 70 ns

s CMOS low power consumption

— 30 mA maximum active current

— 100 µA maximum standby current

— No data retention power consumption

s Compatible with JEDEC-standard byte-wide

32-pin EPROM pinouts

— 32-pin PDIP

— 32-pin PLCC

— 32-pin TSOP

s 100,000 write/erase cycles minimum

s Write and erase voltage 12.0 V ±5%

s Latch-up protected to 100 mA from

–1 V to VCC +1 V

s Embedded Erase Electrical Bulk Chip Erase

— 5 seconds typical chip erase, including

pre-programming

s Embedded Program

— 14 µs typical byte program, including time-out

— 4 seconds typical chip program

s Command register architecture for

microprocessor/microcontroller compatible

write interface

s On-chip address and data latches

s Advanced CMOS flash memory technology

— Low cost single transistor memory cell

s Embedded algorithms for completely self-timed

write/erase operations

GENERAL DESCRIPTION

The Am28F010A is a 1 Megabit Flash memory orga-

nized as 128 Kbytes of 8 bits each. AMD’s Flash memo-

ries offer the most cost-effective and reliable read/write

non-volatile random access memory. The Am28F010A

is packaged in 32-pin PDIP, PLCC, and TSOP versions.

It is designed to be reprogrammed and erased in-system

or in standard EPROM programmers. The Am28F010A

is erased when shipped from the factory.

The standard Am28F010A offers access times of as fast

as 70 ns, allowing high speed microprocessors to

operate without wait states. To eliminate bus contention,

the device has separate chip enable (CE#) and output

enable (OE#) controls.

AMD’s Flash memories augment EPROM functionality

with in-circuit electrical erasure and programming. The

Am28F010A uses a command register to manage this

functionality. The command register allows for 100%

TTL level control inputs and fixed power supply levels

during erase and programming, while maintaining

maximum EPROM compatibility.

The Am28F010A is compatible with the AMD

Am28F256A, Am28F512A, and Am28F020A Flash

memories. All devices in the Am28Fxxx family follow the

JEDEC 32-pin pinout standard. In addition, all devices

Publication# 16778 Rev: D Amendment/+2

Issue Date: May 1998

within this family that offer Embedded Algorithms use

the same command set. This offers designers the flexi-

bility to retain the same device footprint and command

set, at any density between 256 Kbits and 2 Mbits.

AMD’s Flash technology reliably stores memory con-

tents even after 100,000 erase and program cycles. The

AMD cell is designed to optimize the erase and program-

ming mechanisms. In addition, the combination of

advanced tunnel oxide processing and low internal elec-

tric fields for erase and programming operations pro-

duces reliable cycling. The Am28F010A uses a

12.0±5% VPP input to perform the erase and program-

ming functions.

The highest degree of latch-up protection is achieved

with AMD’s proprietary non-epi process. Latch-up pro-

tection is provided for stresses up to 100 mA on address

and data pins from –1 V to VCC +1 V.

AMD’s Flash technology combines years of EPROM and

EEPROM experience to produce the highest levels of

quality, reliability, and cost effectiveness. The

Am28F010A electrically erases all bits simultaneously

using Fowler-Nordheim tunneling. The bytes are

programmed one byte at a time using the EPROM pro-

gramming mechanism of hot electron injection.

1 page

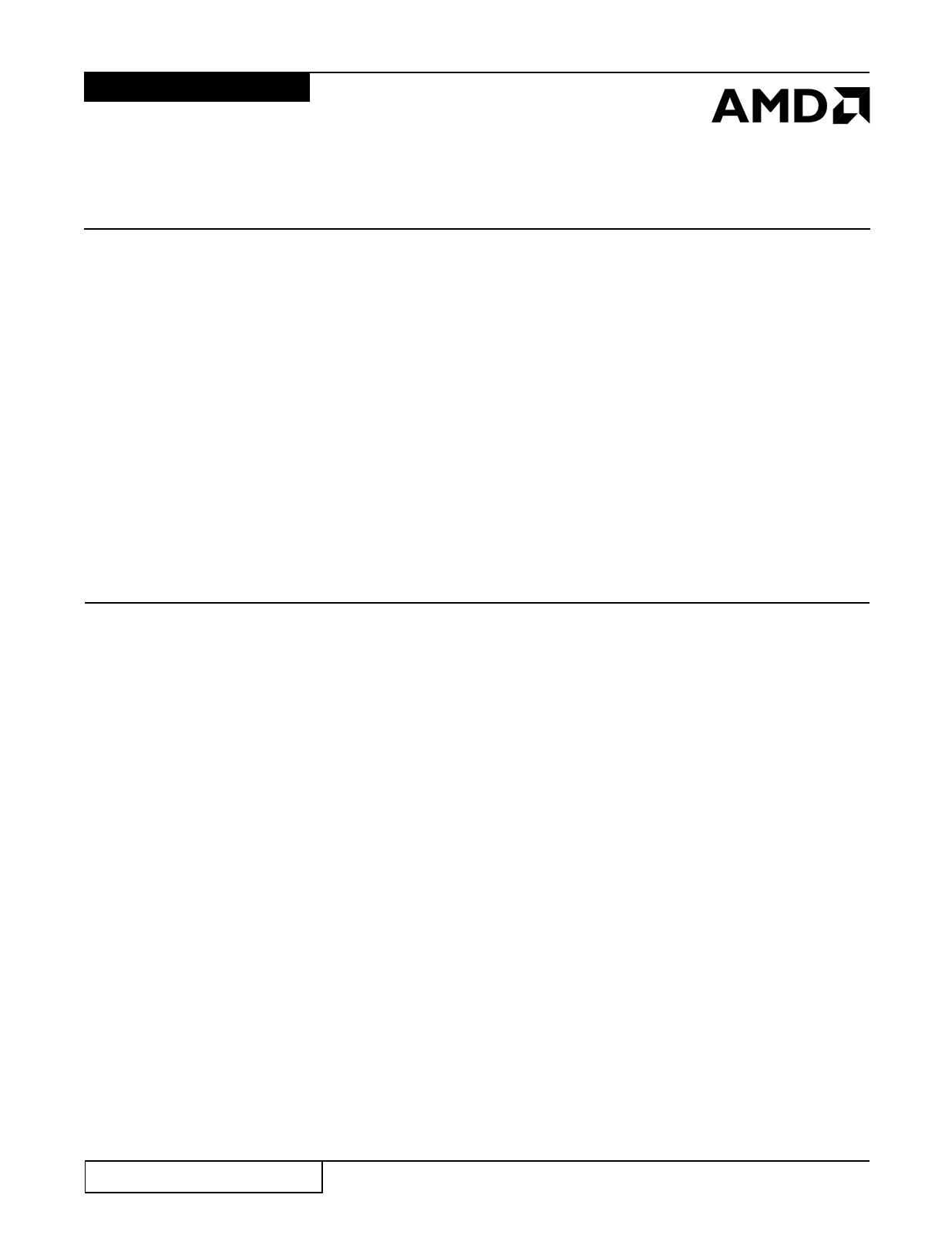

CONNECTION DIAGRAMS (continued)

A11

A9

A8

A13

A14

NC

WE#

VCC

VPP

A16

A15

A12

A7

A6

A5

A4

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

32-Pin TSOP—Standard Pinout

OE#

A10

CE#

D7

D6

D5

D4

D3

VSS

D2

D1

D0

A0

A1

A2

A3

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

32-Pin TSOP—Reverse Pinout

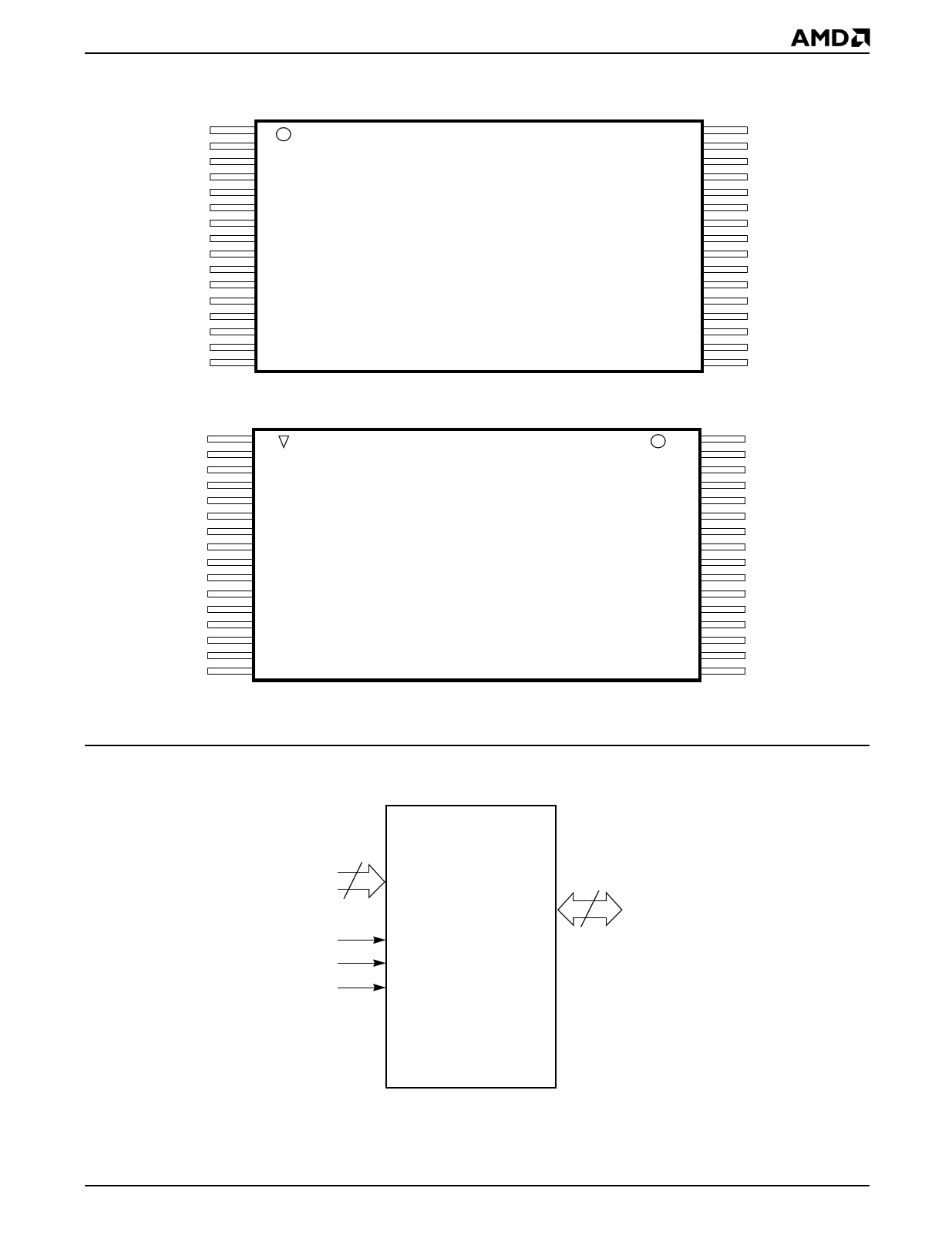

LOGIC SYMBOL

17

A0–A16

DQ0–DQ7

CE# (E#)

OE# (G#)

WE# (W#)

8

32 OE#

31 A10

30 CE#

29 D7

28 D6

27 D5

26 D4

25 D3

24 VSS

23 D2

22 D1

21 D0

20 A0

19 A1

18 A2

17 A3

32 A11

31 A9

30 A8

29 A13

28 A14

27 NC

26 WE#

25 VCC

24 VPP

23 A16

22 A15

21 A12

20 A7

19 A6

18 A5

17 A4

16778D-4

16778D-5

Am28F010A

5

5 Page

ERASE, PROGRAM, AND READ MODE

When VPP is equal to 12.0 V ± 5%, the command reg-

ister is active. All functions are available. That is, the

device can program, erase, read array or autoselect

data, or be standby mode.

Write Operations

High voltage must be applied to the VPP pin in order to

activate the command register. Data written to the reg-

ister serves as input to the internal state machine. The

output of the state machine determines the operational

function of the device.

The command register does not occupy an address-

able memory location. The register is a latch that stores

the command, along with the address and data infor-

mation needed to execute the command. The register

is written by bringing WE# and CE# to VIL, while OE#

is at VIH. Addresses are latched on the falling edge of

WE#, while data is latched on the rising edge of the

WE# pulse. Standard microprocessor write timings are

used.

The device requires the OE# pin to be VIH for write op-

erations. This condition eliminates the possibility for

bus contention during programming operations. In

order to write, OE# must be VIH, and CE# and WE#

must be VIL. If any pin is not in the correct state a write

command will not be executed.

Refer to AC Write Characteristics and the Erase/Pro-

gramming Waveforms for specific timing parameters.

Command Definitions

The contents of the command register default to 00h

(Read Mode) in the absence of high voltage applied to

the VPP pin. The device operates as a read only

memory. High voltage on the VPP pin enables the

command register. Device operations are selected by

writing specific data codes into the command register.

Table 3 in the device data sheet defines these register

commands.

Read Command

Memory contents can be accessed via the read com-

mand when VPP is high. To read from the device, write

00h into the command register. Standard microproces-

sor read cycles access data from the memory. The de-

vice will remain in the read mode until the command

register contents are altered.

The command register defaults to 00h (read mode)

upon VPP power-up. The 00h (Read Mode) register de-

fault helps ensure that inadvertent alteration of the

memory contents does not occur during the VPP power

transition. Refer to the AC Read Characteristics and

Waveforms for the specific timing parameters.

Table 3. Am28F010A Command Definitions

First Bus Cycle

Second Bus Cycle

Command

Operation

(Note 1)

Address

(Note 2)

Data

(Note 3)

Operation

(Note 1)

Address

(Note 2)

Data

(Note 3)

Read Memory (Note 4)

Write

X

00h/FFh

Read

RA

RD

Read Auto select

Write

X

80h or 90h

Read

00h/01h

01h/A2h

Embedded Erase Set-up/

Embedded Erase

Write

X

30h Write

X

30h

Embedded Program Set-up/

Embedded Program

Write

X

10h or 50h

Write

PA

PD

Reset (Note 4)

Write

X

00h/FFh

Write

X 00h/FFh

Notes:

1. Bus operations are defined in Table 1.

2. RA = Address of the memory location to be read.

PA = Address of the memory location to be programmed.

Addresses are latched on the falling edge of the WE# pulse.

X = Don’t care.

3. RD = Data read from location RA during read operation.

PD = Data to be programmed at location PA. Data latched on the rising edge of WE#.

4. Please reference Reset Command section.

Am28F010A

11

11 Page | ||

| Páginas | Total 35 Páginas | |

| PDF Descargar | [ Datasheet AM28F010A-120EC.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| AM28F010A-120EC | 1 Megabit (128 K x 8-Bit) CMOS 12.0 Volt/ Bulk Erase Flash Memory with Embedded Algorithms | Advanced Micro Devices |

| AM28F010A-120ECB | 1 Megabit (128 K x 8-Bit) CMOS 12.0 Volt/ Bulk Erase Flash Memory with Embedded Algorithms | Advanced Micro Devices |

| AM28F010A-120EE | 1 Megabit (128 K x 8-Bit) CMOS 12.0 Volt/ Bulk Erase Flash Memory with Embedded Algorithms | Advanced Micro Devices |

| AM28F010A-120EEB | 1 Megabit (128 K x 8-Bit) CMOS 12.0 Volt/ Bulk Erase Flash Memory with Embedded Algorithms | Advanced Micro Devices |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |