|

|

PDF A290011U-90 Data sheet ( Hoja de datos )

| Número de pieza | A290011U-90 | |

| Descripción | 128K X 8 Bit CMOS 5.0 Volt-only/ Boot Sector Flash Memory | |

| Fabricantes | AMIC Technology | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de A290011U-90 (archivo pdf) en la parte inferior de esta página. Total 30 Páginas | ||

|

No Preview Available !

A29001/290011 Series

Preliminary

128K X 8 Bit CMOS 5.0 Volt-only,

Boot Sector Flash Memory

Features

n 5.0V ± 10% for read and write operations

n Access times:

- 55/70/90 (max.)

n Current:

- 20 mA typical active read current

- 30 mA typical program/erase current

- 1 µA typical CMOS standby

n Flexible sector architecture

- 8 Kbyte/ 4 KbyteX2/ 16 Kbyte/ 32 KbyteX3 sectors

- Any combination of sectors can be erased

- Supports full chip erase

- Sector protection:

A hardware method of protecting sectors to prevent

any inadvertent program or erase operations within

that sector

n Top or bottom boot block configurations available

n Embedded Erase Algorithms

- Embedded Erase algorithm will automatically erase the

entire chip or any combination of designated sectors

and verify the erased sectors

- Embedded Program algorithm automatically writes and

verifies bytes at specified addresses

n Typical 100,000 program/erase cycles per sector

n 20-year data retention at 125°C

- Reliable operation for the life of the system

n Compatible with JEDEC-standards

- Pinout and software compatible with single-power-

supply Flash memory standard

- Superior inadvertent write protection

n Data Polling and toggle bits

- Provides a software method of detecting completion of

program or erase operations

n Erase Suspend/Erase Resume

- Suspends a sector erase operation to read data from,

or program data to, a non-erasing sector, then

resumes the erase operation

n Hardware reset pin (RESET )

- Hardware method to reset the device to reading array

data (not available on A290011)

n Package options

- 32-pin P-DIP, PLCC, or TSOP (Forward type)

General Description

The A29001 is a 5.0 volt-only Flash memory organized as

131,072 bytes of 8 bits each. The A29001 offers the RESET

function, but it is not available on A290011. The 128 Kbytes of

data are further divided into seven sectors for flexible sector

erase capability. The 8 bits of data appear on I/O0 - I/O7 while

the addresses are input on A0 to A16. The A29001 is offered in

32-pin PLCC, TSOP, and PDIP packages. This device is

designed to be programmed in-system with the standard

system 5.0 volt VCC supply. Additional 12.0 volt VPP is not

required for in-system write or erase operations. However, the

A29001 can also be programmed in standard EPROM

programmers.

The A29001 has the first toggle bit, I/O6, which indicates

whether an Embedded Program or Erase is in progress, or it is

in the Erase Suspend. Besides the I/O6 toggle bit, the A29001

has a second toggle bit, I/O2, to indicate whether the

addressed sector is being selected for erase. The A29001 also

offers the ability to program in the Erase Suspend mode. The

standard A29001 offers access times of 55, 70 and 90 ns

allowing high-speed microprocessors to operate without wait

states. To eliminate bus contention the device has separate

chip enable ( CE ), write enable ( WE ) and output enable ( OE )

controls.

The device requires only a single 5.0 volt power supply for both

read and write functions. Internally generated and regulated

voltages are provided for the program and erase operations.

The A29001 is entirely software command set compatible with

the JEDEC single-power-supply Flash standard. Commands

are written to the command register using standard

microprocessor write timings. Register contents serve as input

to an internal state-machine that controls the erase and

programming circuitry. Write cycles also internally latch

addresses and data needed for the programming and erase

operations. Reading data out of the device is similar to reading

from other Flash or EPROM devices.

Device programming occurs by writing the proper program

command sequence. This initiates the Embedded Program

algorithm - an internal algorithm that automatically times the

program pulse widths and verifies proper program margin.

Device erasure occurs by executing the proper erase

command sequence. This initiates the Embedded Erase

algorithm - an internal algorithm that automatically

preprograms the array (if it is not already programmed) before

executing the erase operation. During erase, the device

automatically times the erase pulse widths and verifies proper

erase margin.

PRELIMINARY (August, 2001, Version 0.3)

1

AMIC Technology, Inc.

1 page

A29001/A290011 Series

Requirements for Reading Array Data

To read array data from the outputs, the system must drive

the CE and OE pins to VIL. CE is the power control and

selects the device. OE is the output control and gates

array data to the output pins. WE should remain at VIH all

the time during read operation. The internal state machine

is set for reading array data upon device power-up, or after

a hardware reset. This ensures that no spurious alteration

of the memory content occurs during the power transition.

No command is necessary in this mode to obtain array

data. Standard microprocessor read cycles that assert valid

addresses on the device address inputs produce valid data

on the device data outputs. The device remains enabled for

read access until the command register contents are

altered.

See "Reading Array Data" for more information. Refer to the

AC Read Operations table for timing specifications and to

the Read Operations Timings diagram for the timing

waveforms, lCC1 in the DC Characteristics table represents

the active current specification for reading array data.

Writing Commands/Command Sequences

To write a command or command sequence (which

includes programming data to the device and erasing

sectors of memory), the system must drive WE and CE to

VIL, and OE to VIH. An erase operation can erase one

sector, multiple sectors, or the entire device. The Sector

Address Tables indicate the address range that each sector

occupies. A "sector address" consists of the address inputs

required to uniquely select a sector. See the "Command

Definitions" section for details on erasing a sector or the

entire chip, or suspending/resuming the erase operation.

After the system writes the autoselect command sequence,

the device enters the autoselect mode. The system can

then read autoselect codes from the internal register (which

is separate from the memory array) on I/O7 - I/O0. Standard

read cycle timings apply in this mode. Refer to the

"Autoselect Mode" and "Autoselect Command Sequence"

sections for more information.

ICC2 in the Characteristics table represents the active

current specification for the write mode. The "AC

Characteristics" section contains timing specification tables

and timing diagrams for write operations.

Program and Erase Operation Status

During an erase or program operation, the system may

check the status of the operation by reading the status bits

on I/O7 - I/O0. Standard read cycle timings and ICC read

specifications apply. Refer to "Write Operation Status" for

more information, and to each AC Characteristics section

for timing diagrams.

Standby Mode

When the system is not reading or writing to the device, it

can place the device in the standby mode. In this mode,

current consumption is greatly reduced, and the outputs are

placed in the high impedance state, independent of the OE

input.

The device enters the CMOS standby mode when the CE

& RESET pins ( CE only on A290011) are both held at VCC

± 0.5V. (Note that this is a more restricted voltage range

than VIH.) The device enters the TTL standby mode when

CE is held at VIH, while RESET (Not available on

A290011) is held at VCC±0.5V. The device requires the

standard access time (tCE) before it is ready to read data.

If the device is deselected during erasure or programming,

the device draws active current until the operation is

completed.

ICC3 in the DC Characteristics tables represents the standby

current specification.

Output Disable Mode

When the OE input is at VIH, output from the device is

disabled. The output pins are placed in the high impedance

state.

RESET : Hardware Reset Pin (N/A on A290011)

The RESET pin provides a hardware method of resetting

the device to reading array data. When the system drives

the RESET pin low for at least a period of tRP, the device

immediately terminates any operation in progress, tristates

all data output pins, and ignores all read/write attempts for

the duration of the RESET pulse. The device also resets

the internal state machine to reading array data. The

operation that was interrupted should be reinitiated once

the device is ready to accept another command sequence,

to ensure data integrity.

The RESET pin may be tied to the system reset circuitry. A

system reset would thus also reset the Flash memory,

enabling the system to read the boot-up firmware from the

Flash memory.

Refer to the AC Characteristics tables for RESET

parameters and diagram.

PRELIMINARY (August, 2001, Version 0.3)

5

AMIC Technology, Inc.

5 Page

A29001/A290011 Series

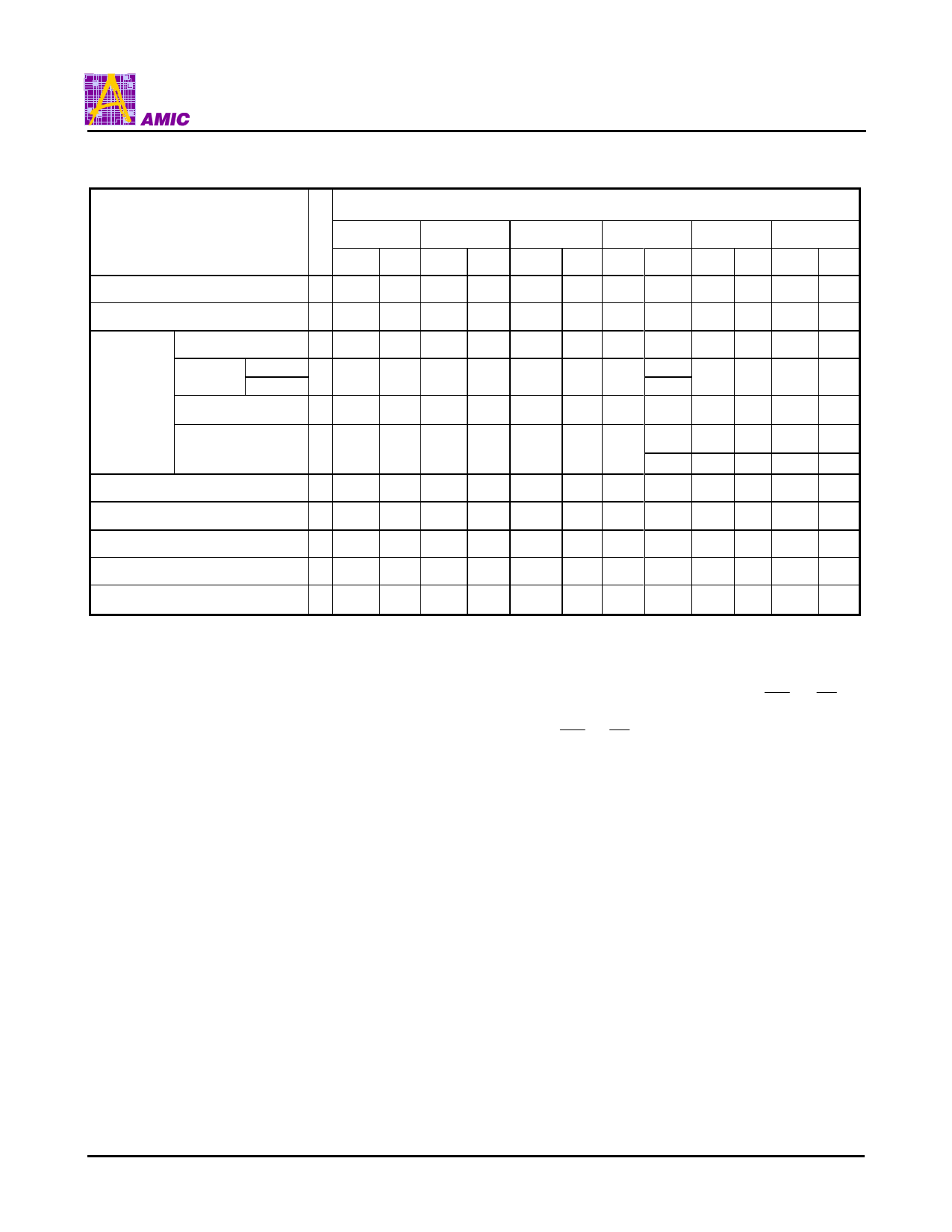

Table 5. A29001/A290011 Command Definitions

Command

Sequence

(Note 1)

Read (Note 5)

First

Second

Addr Data Addr Data

1 RA RD

Reset (Note 6)

1 XXX F0

Manufacturer ID

Autoselect

(Note 7) Device ID Top

Bottom

Continuation ID

4 555 AA

4 555 AA

4 555 AA

2AA 55

2AA 55

2AA 55

Sector Protect Verify 4 555 AA 2AA 55

(Note 8)

Program

Chip Erase

4 555 AA

6 555 AA

2AA 55

2AA 55

Sector Erase

Erase Suspend (Note 9)

Erase Resume (Note 10)

6 555 AA

1 XXX B0

1 XXX 30

2AA 55

Bus Cycles (Notes 2 - 4)

Third

Fourth

Fifth

Sixth

Addr Data Addr Data Addr Data Addr Data

555 90 X00 37

555 90 X01 A1

4C

555 90 X03 7F

555 90 SA 00

X02 01

555 A0 PA PD

555 80 555 AA 2AA 55 555 10

555 80 555 AA 2AA 55 SA 30

Legend:

X = Don't care

RA = Address of the memory location to be read.

RD = Data read from location RA during read operation.

PA = Address of the memory location to be programmed. Addresses latch on the falling edge of the WE or CE pulse,

whichever happens later.

PD = Data to be programmed at location PA. Data latches on the rising edge of WE or CE pulse, whichever happens first.

SA = Address of the sector to be verified (in autoselect mode) or erased. Address bits A16 - A12 select a unique sector.

Note:

1. See Table 1 for description of bus operations.

2. All values are in hexadecimal.

3. Except when reading array or autoselect data, all bus cycles are write operation.

4. Address bits A16 - A12 are don't cares for unlock and command cycles, unless SA or PA required.

5. No unlock or command cycles required when reading array data.

6. The Reset command is required to return to reading array data when device is in the autoselect mode, or if I/O5 goes high

(while the device is providing status data).

7. The fourth cycle of the autoselect command sequence is a read cycle.

8. The data is 00h for an unprotected sector and 01h for a protected sector. See "Autoselect Command Sequence" for more

information.

9. The system may read and program in non-erasing sectors, or enter the autoselect mode, when in the Erase Suspend

mode.

10. The Erase Resume command is valid only during the Erase Suspend mode.

11. The time between each command cycle has to be less than 50µs.

PRELIMINARY (August, 2001, Version 0.3)

11

AMIC Technology, Inc.

11 Page | ||

| Páginas | Total 30 Páginas | |

| PDF Descargar | [ Datasheet A290011U-90.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| A290011U-90 | 128K X 8 Bit CMOS 5.0 Volt-only/ Boot Sector Flash Memory | AMIC Technology |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |