|

|

PDF SZESD7462 Data sheet ( Hoja de datos )

| Número de pieza | SZESD7462 | |

| Descripción | Ultra-Low Capacitance ESD Protection | |

| Fabricantes | ON Semiconductor | |

| Logotipo | ||

Hay una vista previa y un enlace de descarga de SZESD7462 (archivo pdf) en la parte inferior de esta página. Total 6 Páginas | ||

|

No Preview Available !

ESD7462, SZESD7462

Ultra-Low Capacitance ESD

Protection

Micro−Packaged Diodes for ESD Protection

The ESD7462 is designed to protect voltage sensitive components

that require ultra−low capacitance from ESD and transient voltage

events. It has industry leading capacitance linearity over voltage

making it ideal for RF applications. This capacitance linearity

combined with the extremely small package and low insertion loss

makes this part well suited for use in antenna line applications for

wireless handsets and terminals.

Features

• Industry Leading Capacitance Linearity Over Voltage

• Ultra−Low Capacitance: 0.3 pF Typ

• Insertion Loss: 0.05 dB at 1 GHz; 0.10 dB at 3 GHz

• Low Leakage: < 1 nA Typ

• Protection for the following IEC Standards:

♦ IEC61000−4−2 (ESD): Level 4

♦ IEC61000−4−4 (EFT): 40 A −5/50 ns

♦ IEC61000−4−5 (Lightning): 1 A (8/20 ms)

• Protection for ISO 10605 (ESD)

• SZ Prefix for Automotive and Other Applications Requiring Unique

Site and Control Change Requirements; AEC−Q101 Qualified and

PPAP Capable

• These Devices are Pb−Free, Halogen Free/BFR Free and are RoHS

Compliant

Typical Applications

• RF Signal ESD Protection

• RF Switching, PA, and Antenna ESD Protection

• Near Field Communications

• USB 2.0, USB 3.0

MAXIMUM RATINGS (TA = 25°C unless otherwise noted)

Rating

Symbol Value

Unit

IEC 61000−4−2 Contact (Note 1)

IEC 61000−4−2 Air

ISO 10605 Contact (330 pF / 330 W)

ISO 10605 Contact (330 pF / 2 kW)

ISO 10605 Contact (150 pF / 2 kW)

ESD ±18 kV

±18

±13

±29

±30

Total Power Dissipation (Note 2) @ TA = 25°C

Thermal Resistance, Junction−to−Ambient

Junction and Storage Temperature Range

°PD°

RqJA

TJ, Tstg

300

400

−55 to

+150

mW

°C/W

°C

Lead Solder Temperature − Maximum

(10 Second Duration)

TL 260 °C

Stresses exceeding those listed in the Maximum Ratings table may damage the

device. If any of these limits are exceeded, device functionality should not be

assumed, damage may occur and reliability may be affected.

1. Non−repetitive current pulse at TA = 25°C, per IEC61000−4−2 waveform.

2. Mounted with recommended minimum pad size, DC board FR−4

www.onsemi.com

X2DFN2

CASE 714AB

MARKING

DIAGRAM

4M

G

4 = Specific Device Code

M = Date Code

ORDERING INFORMATION

Device

Package

Shipping†

ESD7462N2T5G

X2DFN2 8000 / Tape &

(Pb−Free)

Reel

SZESD7462N2T5G X2DFN2 8000 / Tape &

(Pb−Free)

Reel

†For information on tape and reel specifications,

including part orientation and tape sizes, please

refer to our Tape and Reel Packaging Specifications

Brochure, BRD8011/D.

© Semiconductor Components Industries, LLC, 2016

January, 2017 − Rev. 1

1

Publication Order Number:

ESD7462/D

1 page

ESD7462, SZESD7462

20 10 −20 −10

18 −18

16 8 −16 −8

14 −14

12 6 −12 −6

10 −10

8 4 −8 −4

6 −6

4 2 −4 −2

2 −2

0 00 0

0 10 20 30 40 50 60

0 −10 −20 −30 −40 −50 −60

VC, CLAMPING VOLTAGE (V)

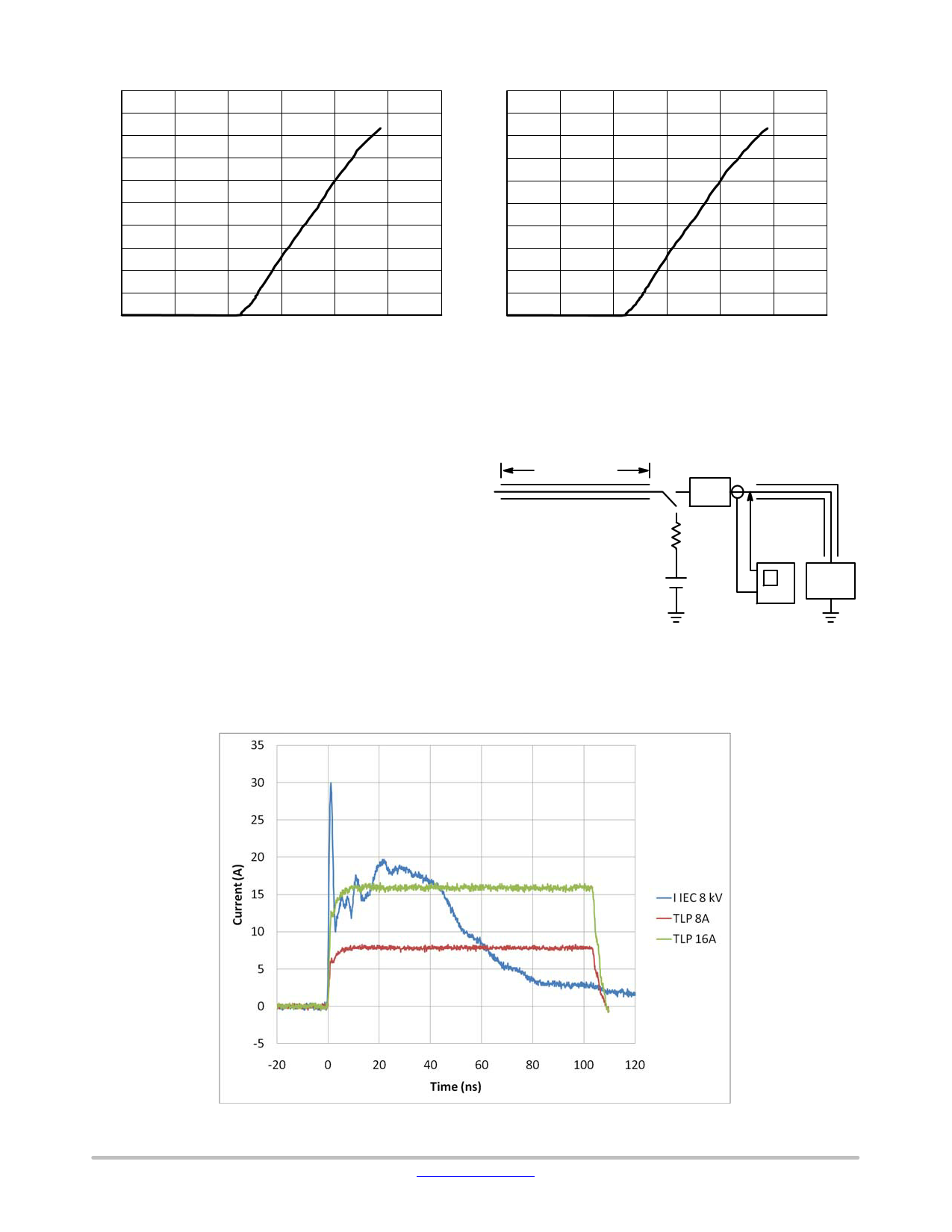

Figure 9. Typical Positive TLP IV Curve

VC, CLAMPING VOLTAGE (V)

Figure 10. Typical Negative TLP IV Curve

NOTE: TLP parameter: Z0 = 50 W, tp = 100 ns, tr = 300 ps, averaging window: t1 = 30 ns to t2 = 60 ns. VIEC is the equivalent voltage

stress level calculated at the secondary peak of the IEC 61000−4−2 waveform at t = 30 ns with 2 A/kV. See TLP description

below for more information.

Transmission Line Pulse (TLP) Measurement

Transmission Line Pulse (TLP) provides current versus

voltage (I−V) curves in which each data point is obtained

from a 100 ns long rectangular pulse from a charged

transmission line. A simplified schematic of a typical TLP

system is shown in Figure 11. TLP I−V curves of ESD

protection devices accurately demonstrate the product’s

ESD capability because the 10s of amps current levels and

under 100 ns time scale match those of an ESD event. This

is illustrated in Figure 12 where an 8 kV IEC 61000−4−2

current waveform is compared with TLP current pulses at

8 A and 16 A. A TLP I−V curve shows the voltage at which

the device turns on as well as how well the device clamps

voltage over a range of current levels.

L

50 W Coax

Cable

S Attenuator

÷

50 W Coax

Cable

10 MW

IM VM

VC DUT

Oscilloscope

Figure 11. Simplified Schematic of a Typical TLP

System

Figure 12. Comparison Between 8 kV IEC 61000−4−2 and 8 A and 16 A TLP Waveforms

www.onsemi.com

5

5 Page | ||

| Páginas | Total 6 Páginas | |

| PDF Descargar | [ Datasheet SZESD7462.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| SZESD7461 | Ultra-Low Capacitance ESD Protection | ON Semiconductor |

| SZESD7462 | Ultra-Low Capacitance ESD Protection | ON Semiconductor |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |