|

|

PDF MPC5675K Data sheet ( Hoja de datos )

| Número de pieza | MPC5675K | |

| Descripción | Microcontroller | |

| Fabricantes | Freescale Semiconductor | |

| Logotipo | ||

Hay una vista previa y un enlace de descarga de MPC5675K (archivo pdf) en la parte inferior de esta página. Total 30 Páginas | ||

|

No Preview Available !

Freescale Semiconductor

Data Sheet: Technical Data

Document Number: MPC5675K

Rev. 7, 5/2012

Qorivva MPC5675K

Microcontroller Data Sheet

MPC5675K

MAPBGA–225

15 mm x 15 mm

QFN12

##_mm_x_##mm

1 Introduction

1.1 Document overview

This document provides electrical specifications, pin

assignments, and package diagrams for the Qorivva

MPC5675K series of microcontroller units (MCUs).

1.2 Description

The Qorivva MPC5675K microcontroller, a SafeAssure

solution, is a 32-bit embedded controller designed for

advanced driver assistance systems with RADAR, CMOS

imaging, LIDAR and ultrasonic sensors, and multiple 3-phase

motor control applications as in hybrid electric vehicles

(HEV) in automotive and high temperature industrial

applications.

A member of Freescale Semiconductor’s Qorivva

MPC5500/5600 family, it contains the Book E compliant

Power Architecture technology core with Variable Length

Encoding (VLE). This core complies with the Power

Architecture embedded category, and is 100 percent user

mode compatible with the original Power PC user

instruction set architecture (UISA). It offers system

performance up to four times that of its MPC5561

predecessor, while bringing you the reliability and familiarity

of the proven Power Architecture technology.

A comprehensive suite of hardware and software

development tools is available to help simplify and speed

system design. Development support is available from

leading tools vendors providing compilers, debuggers and

simulation development environments.

SOT-343R

PKG-TBD

##_mm_x_##mm

473 MAPBGA

(19 x 19 mm)

TBD ## mm x ## mm

257 MAPBGA

(14 x 14 mm)

1 Introduction. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1

1.1 Document overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1

1.2 Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1

1.3 Device comparison . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2

1.4 Block diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5

1.5 Feature list . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6

1.6 Feature details . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7

2 Package pinouts and signal descriptions . . . . . . . . . . . . . . . . 17

2.1 Package pinouts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

2.2 Pin descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20

3 Electrical characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 69

3.1 Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 69

3.2 Absolute maximum ratings . . . . . . . . . . . . . . . . . . . . . . 69

3.3 Recommended operating conditions . . . . . . . . . . . . . . 70

3.4 Thermal characteristics . . . . . . . . . . . . . . . . . . . . . . . . 72

3.5 Electromagnetic interference (EMI) characteristics . . . 73

3.6 Electrostatic discharge (ESD) characteristics. . . . . . . . 74

3.7 Static latch-up (LU) . . . . . . . . . . . . . . . . . . . . . . . . . . . . 74

3.8 Power Management Controller (PMC) electrical

characteristics. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 74

3.9 Supply current characteristics. . . . . . . . . . . . . . . . . . . . 76

3.10 Temperature sensor electrical characteristics. . . . . . . . 77

3.11 Main oscillator electrical characteristics . . . . . . . . . . . . 77

3.12 FMPLL electrical characteristics . . . . . . . . . . . . . . . . . . 78

3.13 16 MHz RC oscillator electrical characteristics. . . . . . . 79

3.14 ADC electrical characteristics . . . . . . . . . . . . . . . . . . . . 79

3.15 Flash memory electrical characteristics . . . . . . . . . . . . 84

3.16 SRAM memory electrical characteristics . . . . . . . . . . . 86

3.17 GP pads specifications . . . . . . . . . . . . . . . . . . . . . . . . . 87

3.18 PDI pads specifications . . . . . . . . . . . . . . . . . . . . . . . . 88

3.19 DRAM pad specifications . . . . . . . . . . . . . . . . . . . . . . . 90

3.20 RESET characteristics . . . . . . . . . . . . . . . . . . . . . . . . . 96

3.21 Reset sequence . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 96

3.22 Peripheral timing characteristics . . . . . . . . . . . . . . . . . 102

4 Package characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . 126

4.1 Package mechanical data. . . . . . . . . . . . . . . . . . . . . . 126

5 Orderable parts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 132

6 Reference documents . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 132

7 Document revision history . . . . . . . . . . . . . . . . . . . . . . . . . . 132

© Freescale Semiconductor, Inc., 2009–2012. All rights reserved.

1 page

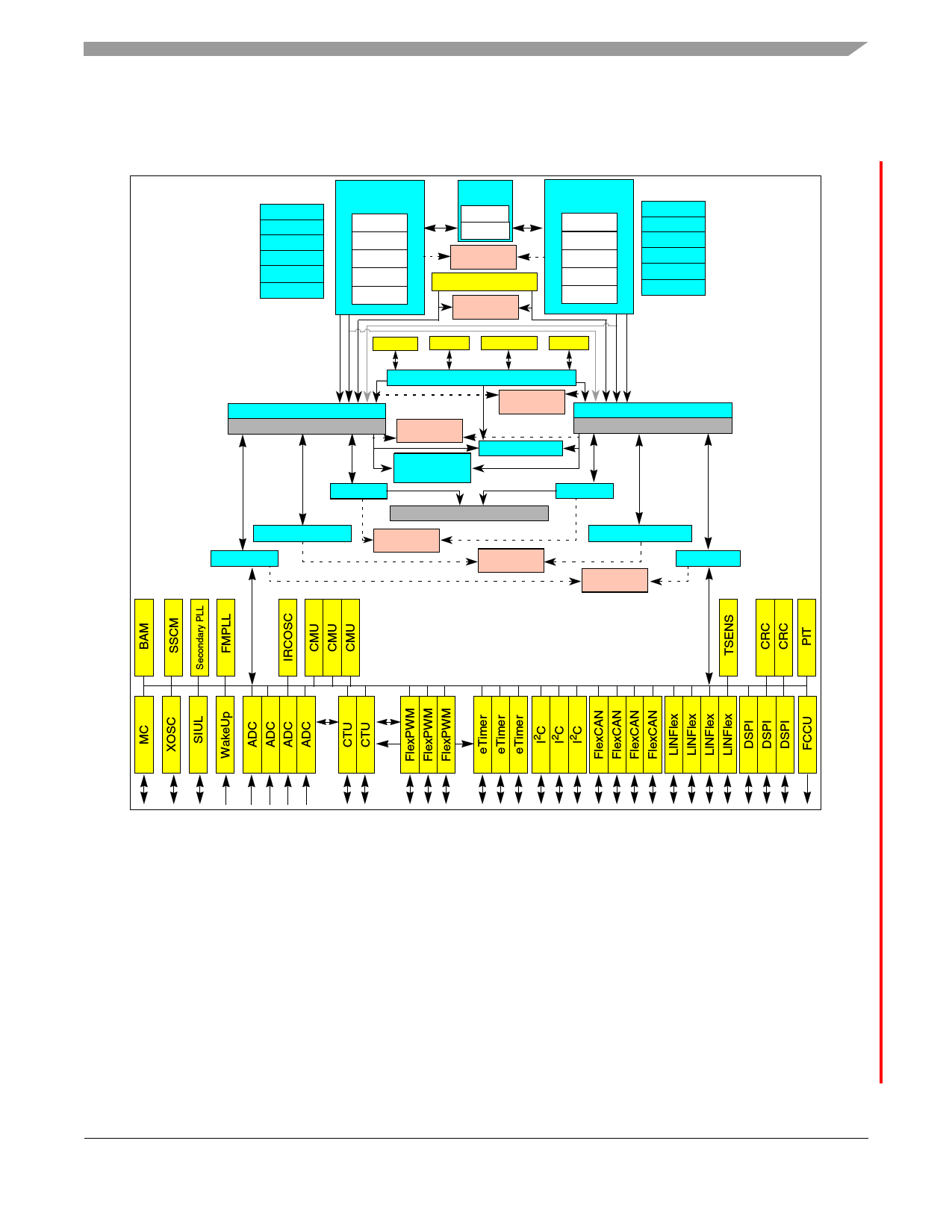

1.4 Block diagram

Figure 1 shows a top-level block diagram of the MPC5675K device.

PMC

ECSM_0

STM

SWT_0

INTC

SEMA4

e200z7d

Core_1

SPE2

VLE

MMU

I-CACHE

D-CACHE

DMA_0

Debug

JTAG

Nexus

Redundancy

Checker[0]

FlexRay

Redundancy

Checker[5]

e200z7d

Core_1

SPE2

VLE

MMU

I-CACHE

D-CACHE

PDI Ethernet DMA_1

PMC

ECSM_1

STM

SWT_1

INTC

SEMA4

Crossbar switch (XBAR_0)

Memory protection unit

PFLASHC

Crossbar switch (XBAR_2)

Redundancy

Checker[6]

External Bus

Interface

Redundancy

Checker[7]

DDR Controller

Crossbar switch (XBAR_1)

Memory protection unit

PFLASHC

2MB Flash with ECC Logic

SRAM with ECC Logic

PBPBRRIDIDGGEE

Redundancy

Checker[3]

Redundancy

Checker[4]

SRAM with ECC Logic

Redundancy

Checker[2]

PBRIDGE

Introduction

ADC

– Analog-to-digital converter

BAM

– Boot assist module

CMU

– Clock monitoring unit

CRC

– Cyclic redundancy check unit

CTU

– Cross triggering unit

DSPI

– Deserial serial peripheral interface

EBI – External bus interface

ECC

– Error correction code

ECSM – Error correction status module

eDMA – Enhanced direct memory access controller

FCCU – Fault collection and control unit

FEC

– Fast Ethernet controller

FlexCAN – Controller area network controller

FlexPWM – Pulse width modulator module

FMPLL – Frequency-modulated phase-locked loop

I2C – Inter-integrated circuit controller

INTC

– Interrupt controller

IRCOSC – Internal RC oscillator

JTAG

– Joint Test Action Group interface

MC – Mode entry, clock, reset, and power modules

mDDR – Mobile double data rate dynamic RAM

PBRIDGE – Peripheral bridge

PDI – Parallel data interface

PIT – Periodic interrupt timer

PMC

– Power management controller

RC – Redundancy checker

RTC

– Real time clock

SEMA4 – Semaphore unit

SIUL

– System integration unit Lite

SSCM – System status and configuration module

STM

– System timer module

SWT

– Software watchdog timer

TSENS – Temperature sensor

XOSC – Crystal oscillator

Figure 1. MPC5675K block diagram

MPC5675K Microcontroller Data Sheet, Rev. 7

Freescale Semiconductor

5

5 Page

— Modified SPI mode for interfacing to peripherals with longer setup time requirements

• Support for up to 60 Mbit/s in slave only Rx mode

Introduction

1.6.15 Serial Communication Interface Module (LINFlex)

The LINFlex on this device features the following:

• Supports LIN Master mode, LIN Slave mode, and UART mode

• LIN state machine compliant to LIN1.3, 2.0, and 2.1 specifications

• Manages LIN frame transmission and reception without CPU intervention

• LIN features

— Autonomous LIN frame handling

— Message buffer to store as many as 8 data bytes

— Supports messages as long as 64 bytes

— Detection and flagging of LIN errors (Sync field, delimiter, ID parity, bit framing, checksum and timeout errors)

— Classic or extended checksum calculation

— Configurable break duration of up to 36-bit times

— Programmable baud rate prescalers (13-bit mantissa, 4-bit fractional)

— Diagnostic features (loop back, LIN bus stuck dominant detection)

— Interrupt-driven operation with 16 interrupt sources

• LIN slave mode features

— Autonomous LIN header handling

— Autonomous LIN response handling

• UART mode

— Full-duplex operation

— Standard non return-to-zero (NRZ) mark/space format

— Data buffers with 4-byte receive, 4-byte transmit

— Configurable word length (8-bit, 9-bit, or 16-bit words)

— Configurable parity scheme: none, odd, even, always 0

— Speed as fast as 2 Mbit/s

— Error detection and flagging (parity, noise, and framing errors)

— Interrupt-driven operation with four interrupt sources

— Separate transmitter and receiver CPU interrupt sources

— 16-bit programmable baud-rate modulus counter and 16-bit fractional

— Two receiver wake-up methods

• Support for DMA-enabled transfers

1.6.16 FlexCAN

• Thirty-two message buffers each

• Full implementation of the CAN protocol specification, Version 2.0B

• Programmable acceptance filters

• Individual Rx filtering per message buffer

• Short latency time for high priority transmit messages

• Arbitration scheme according to message ID or message buffer number

• Listen-only mode capabilities

• Programmable clock source: system clock or oscillator clock

Freescale Semiconductor

MPC5675K Microcontroller Data Sheet, Rev. 7

11

11 Page | ||

| Páginas | Total 30 Páginas | |

| PDF Descargar | [ Datasheet MPC5675K.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| MPC5675K | Microcontroller | Freescale Semiconductor |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |