|

|

PDF CY15B101N Data sheet ( Hoja de datos )

| Número de pieza | CY15B101N | |

| Descripción | 1-Mbit (64K x 16) Automotive F-RAM Memory | |

| Fabricantes | Cypress Semiconductor | |

| Logotipo | ||

Hay una vista previa y un enlace de descarga de CY15B101N (archivo pdf) en la parte inferior de esta página. Total 19 Páginas | ||

|

No Preview Available !

CY15B101N

1-Mbit (64K × 16) Automotive F-RAM Memory

1-Mbit (64K × 16) Automotive F-RAM Memory

Features

■ 1-Mbit ferroelectric random access memory (F-RAM™)

logically organized as 64K × 16

❐ Configurable as 128K × 8 using UB and LB

❐ High-endurance 100 trillion (1014) read/writes

❐ 151-year data retention (see the Data Retention and

Endurance table)

❐ NoDelay™ writes

❐ Page-mode operation for 30-ns cycle time

❐ Advanced high-reliability ferroelectric process

■ SRAM compatible

❐ Industry-standard 64K × 16 SRAM pinout

❐ 60-ns access time, 90-ns cycle time

■ Superior to battery-backed SRAM modules

❐ No battery concerns

❐ Monolithic reliability

❐ True surface-mount solution, no rework steps

❐ Superior for moisture, shock, and vibration

■ Low power consumption

❐ Active current 7 mA (typ)

❐ Standby current 120 A (typ)

■ Low-voltage operation: VDD = 2.0 V to 3.6 V

■ Automotive-A temperature: –40 C to +85 C

Logic Block Diagram

■ 44-pin thin small outline package (TSOP) Type II

■ Restriction of hazardous substances (RoHS)-compliant

Functional Description

The CY15B101N is a 64K × 16 nonvolatile memory that reads

and writes similar to a standard SRAM. A ferroelectric random

access memory or F-RAM is nonvolatile, which means that data

is retained after power is removed. It provides data retention for

over 151 years while eliminating the reliability concerns,

functional disadvantages, and system design complexities of

battery-backed SRAM (BBSRAM). Fast write-timing and high

write-endurance make the F-RAM superior to other types of

memory.

The CY15B101N operation is similar to that of other RAM

devices, and, therefore, it can be used as a drop-in replacement

for a standard SRAM in a system. Read cycles may be triggered

by CE or simply by changing the address and write cycles may

be triggered by CE or WE. The F-RAM memory is nonvolatile

due to its unique ferroelectric memory process. These features

make the CY15B101N ideal for nonvolatile memory applications

requiring frequent or rapid writes.

The device is available in a 400-mil, 44-pin TSOP-II

surface-mount package. Device specifications are guaranteed

over the Automotive-A temperature range –40 °C to +85 °C.

For a complete list of related resources, click here.

A15-0

A15-2

A1-0

CE

WE

UB, LB

OE

ZZ

Control

Logic

64K x 16 block

F-RAM Array

...

Column Decoder

I/O Latch & Bus Driver

DQ15-0

Cypress Semiconductor Corporation • 198 Champion Court

Document Number: 001-96058 Rev. *D

• San Jose, CA 95134-1709 • 408-943-2600

Revised September 4, 2015

1 page

CY15B101N

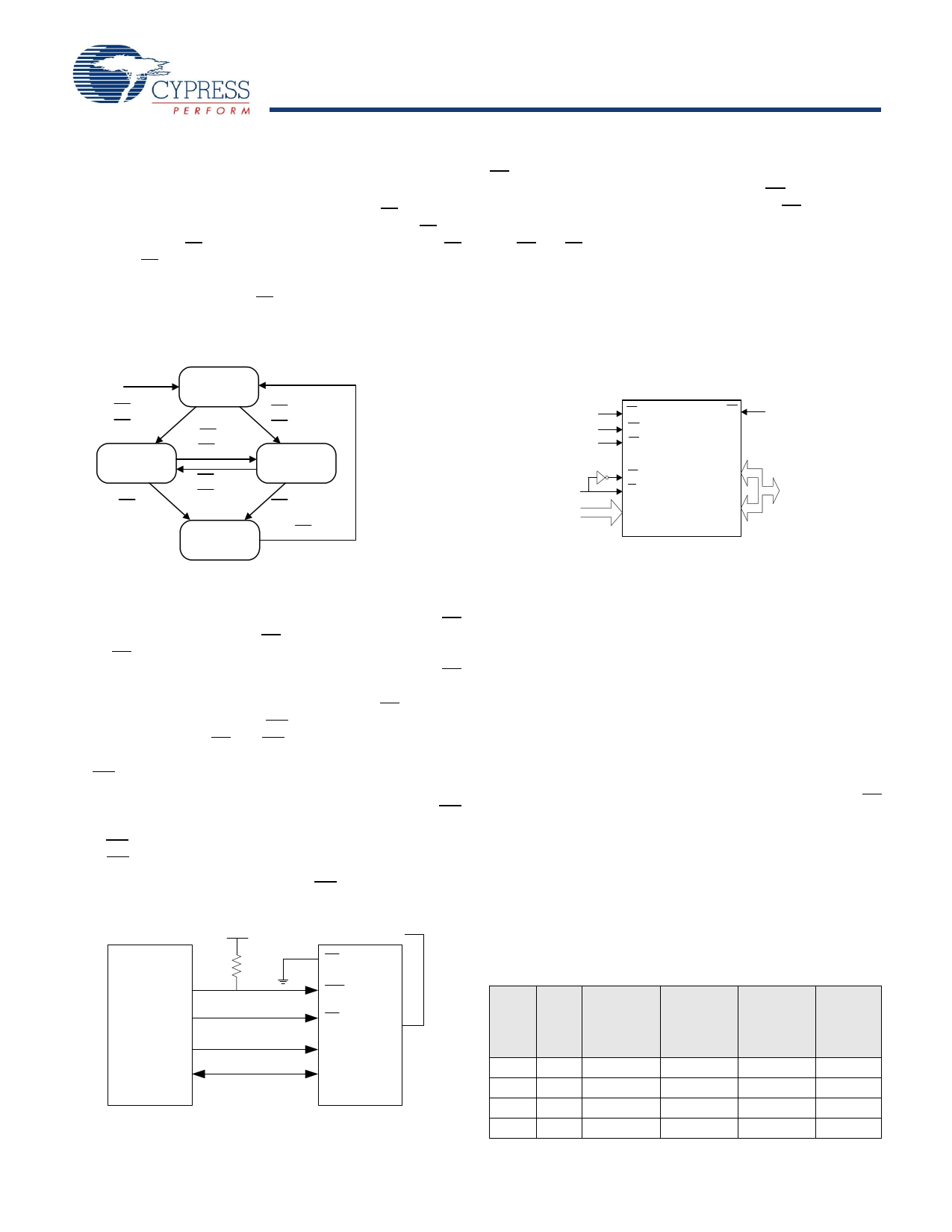

Sleep Mode

The device incorporates a sleep mode of operation, which allows

the user to achieve the lowest-power-supply-current condition. It

enters a low-power sleep mode by asserting the ZZ pin LOW.

Read and write operations must complete before the ZZ pin

going LOW. When ZZ is LOW, all pins are ignored except the ZZ

pin. When ZZ is deasserted HIGH, there is some time delay

(tZZEX) before the user can access the device.

If sleep mode is not used, the ZZ pin must be tied to VDD.

Figure 2. Sleep/Standby State Diagram

Power

Applied

CE HIGH,

ZZ HIGH

Standby

ZZ LOW

Initialize

CE LOW,

ZZ HIGH

CE HIGH,

ZZ HIGH

CE LOW,

ZZ HIGH

Normal

Operation

ZZ LOW

Sleep

ZZ HIGH

SRAM Drop-In Replacement

The CY15B101N is designed to be a drop-in replacement for

standard asynchronous SRAMs. The device does not require CE

to toggle for each new address. CE may remain LOW indefinitely.

While CE is LOW, the device automatically detects address

changes and a new access begins. This functionality allows CE

to be grounded, similar to an SRAM. It also allows page mode

operation at speeds up to 33 MHz. Note that if CE is tied to

ground, the user must be sure WE is not LOW at power-up or

power-down events. If CE and WE are both LOW during power

cycles, data will be corrupted. Figure 3 shows a pull-up resistor

on WE, which will keep the pin HIGH during power cycles,

assuming the MCU/MPU pin tristates during the reset condition.

The pull-up resistor value should be chosen to ensure the WE

pin tracks VDD to a high enough value, so that the current drawn

when WE is LOW is not an issue. A 10-k resistor draws 330 µA

when WE is LOW and VDD = 3.3 V.

Figure 3. Use of Pull-up Resistor on WE

VDD

MCU / MPU

CY15B 101N

CE

WE

OE

A15-0

DQ15-0

For applications that require the lowest power consumption, the

CE signal should be active (LOW) only during memory accesses.

The CY15B101N draws supply current while CE is LOW, even if

addresses and control signals are static. While CE is HIGH, the

device draws no more than the maximum standby current, ISB.

The UB and LB byte select pins are active for both read and write

cycles. They may be used to allow the device to be wired as a

128K × 8 memory. The upper and lower data bytes can be tied

together and controlled with the byte selects. Individual byte

enables or the next higher address line A16 may be available

from the system processor.

Figure 4. CY15B101N Wired as 128 K x 8

A16

A15-0

CE ZZ

WE 1-Mbit F-RAM

OE CY15B101N

UB

LB

A15-0

DQ15-8

DQ7-0

D7-0

Endurance

The CY15B101N is capable of being accessed at least 1014

times – reads or writes. An F-RAM memory operates with a read

and restore mechanism. Therefore, an endurance cycle is

applied on a row basis. The F-RAM architecture is based on an

array of rows and columns. Rows are defined by A15-2 and

column addresses by A1-0. The array is organized as 16K rows

of four words each. The entire row is internally accessed once

whether a single 16-bit word or all four words are read or written.

Each word in the row is counted only once in an endurance

calculation.

The user may choose to write CPU instructions and run them

from a certain address space. Table 1 shows endurance

calculations for a 256-byte repeating loop, which includes a

starting address, three-page mode accesses, and a CE

precharge. The number of bus clock cycles needed to complete

a four-word transaction is 4 + 1 at lower bus speeds, but 5 + 2 at

33 MHz due to initial read latency and an extra clock cycle to

satisfy the device's precharge timing constraint tPC. The entire

loop causes each byte to experience only one endurance cycle.

The F-RAM read and write endurance is virtually unlimited even

at a 33-MHz system bus clock rate.

Table 1. Time to Reach 100 Trillion Cycles for Repeating

256-byte Loop

Bus

Freq

(MHz)

33

25

10

5

Bus

Cycle

Time

(ns)

256-byte

Transaction

Time (s)

30 10.56

40 12.8

100 28.8

200 57.6

Endurance

Cycles/sec

94,690

78,125

34,720

17,360

Endurance

Cycles/year

2.98 x 1012

2.46 x 1012

1.09 x 1012

5.47 x 1011

Years to

Reach

1014

Cycles

33.5

40.6

91.7

182.8

Document Number: 001-96058 Rev. *D

Page 5 of 19

5 Page

CY15B101N

CE

A15-0

WE

DQ15-0

Figure 8. Write Cycle Timing 1 (WE Controlled) [8]

tCA

tCW

tPC

tAS tWLC

tWZ

D out

tWP

tDH

tDS

D in

tWX

tHZ

D out

CE

A15-0

Figure 9. Write Cycle Timing 2 (CE Controlled)

tCA tPC

tAS tBLC

WE

DQ15-0

UB/LB

tDS

D in

tDH

A15-0

WE

DQ15-0

Figure 10. Write Cycle Timing 3 (CE LOW) [8]

tWC

tAWH

tWZ

D out

tWLA

tDS

D in

tWX

tDH

D out

D in

Note

8. OE (not shown) is LOW only to show the effect of WE on DQ pins.

Document Number: 001-96058 Rev. *D

Page 11 of 19

11 Page | ||

| Páginas | Total 19 Páginas | |

| PDF Descargar | [ Datasheet CY15B101N.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| CY15B101N | 1-Mbit (64K x 16) Automotive F-RAM Memory | Cypress Semiconductor |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |