|

|

PDF CY7C1444AV33 Data sheet ( Hoja de datos )

| Número de pieza | CY7C1444AV33 | |

| Descripción | 36-Mbit Pipelined DCD Sync SRAM | |

| Fabricantes | Cypress Semiconductor | |

| Logotipo | ||

Hay una vista previa y un enlace de descarga de CY7C1444AV33 (archivo pdf) en la parte inferior de esta página. Total 24 Páginas | ||

|

No Preview Available !

CY7C1444AV33

36-Mbit (1M × 36) Pipelined DCD Sync

SRAM

36-Mbit (1M × 36) Pipelined DCD Sync SRAM

Features

■ Supports bus operation up to 250 MHz

■ Available speed grades are 250 MHz and 167 MHz

■ Registered inputs and outputs for pipelined operation

■ Optimal for performance (double-cycle deselect)

■ Depth expansion without wait state

■ 3.3 V core power supply

■ 2.5 V/3.3 V I/O power supply

■ Fast clock-to-output times

❐ 2.6 ns (for 250-MHz device)

■ Provide high-performance 3-1-1-1 access rate

■ User-selectable burst counter supporting Intel Pentium

interleaved or linear burst sequences

■ Separate processor and controller address strobes

■ Synchronous self-timed writes

■ Asynchronous output enable

■ CY7C1444AV33 available in JEDEC-standard Pb-free 100-pin

TQFP package

■ “ZZ” sleep mode option

Functional Description

The CY7C1444AV33 SRAM integrates 1M × 36 SRAM cells with

advanced synchronous peripheral circuitry and a two-bit counter

for internal burst operation. All synchronous inputs are gated by

registers controlled by a positive-edge-triggered clock input

(CLK). The synchronous inputs include all addresses, all data

inputs, address-pipelining chip enable (CE1), depth-expansion

chip enables (CE2 and CE3), burst control inputs (ADSC, ADSP,

and ADV), write enables (BWX, and BWE), and global write

(GW). Asynchronous inputs include the output enable (OE) and

the ZZ pin.

Addresses and chip enables are registered at rising edge of

clock when either address strobe processor (ADSP) or address

strobe controller (ADSC) are active. Subsequent burst

addresses can be internally generated as controlled by the

advance pin (ADV).

Address, data inputs, and write controls are registered on-chip

to initiate a self-timed write cycle. This part supports byte write

operations (see Pin Descriptions and Truth Table for further

details). Write cycles can be one to four bytes wide as controlled

by the byte write control inputs. GW active LOW causes all bytes

to be written. This device incorporates an additional pipelined

enable register which delays turning off the output buffers an

additional cycle when a deselect is executed. This feature allows

depth expansion without penalizing system performance.

The CY7C1444AV33 operates from a +3.3 V core power supply

while all outputs operate with a +3.3 V or a +2.5 V supply. All

inputs and outputs are JEDEC-standard JESD8-5-compatible.

For a complete list of related documentation, click here.

Selection Guide

Maximum access time

Maximum operating current

Maximum CMOS standby current

Description

250 MHz

2.6

475

120

167 MHz

3.4

375

120

Unit

ns

mA

mA

Cypress Semiconductor Corporation • 198 Champion Court

Document Number: 38-05352 Rev. *N

• San Jose, CA 95134-1709 • 408-943-2600

Revised November 2, 2016

1 page

CY7C1444AV33

Pin Definitions

Name

I/O

Description

A0, A1, A

Input- Address inputs used to select one of the address locations. Sampled at the rising edge of the CLK

synchronous if ADSP or ADSC is active LOW, and CE1, CE2, and CE3 are sampled active. A1:A0 are fed to the

two-bit counter.

BWA, BWB,

BWC, BWD

GW

BWE

Input- Byte write select inputs, active LOW. Qualified with BWE to conduct byte writes to the SRAM.

synchronous Sampled on the rising edge of CLK.

Input- Global write enable input, active LOW. When asserted LOW on the rising edge of CLK, a global write

synchronous is conducted (all bytes are written, regardless of the values on BWX and BWE).

Input- Byte write enable input, active LOW. Sampled on the rising edge of CLK. This signal must be asserted

synchronous LOW to conduct a byte write.

CLK Input- Clock input. Used to capture all synchronous inputs to the device. Also used to increment the burst

clock counter when ADV is asserted LOW, during a burst operation.

CE1 Input- Chip enable 1 input, active LOW. Sampled on the rising edge of CLK. Used in conjunction with CE2

synchronous and CE3 to select/deselect the device. ADSP is ignored if CE1 is HIGH. CE1 is sampled only when a

new external address is loaded.

CE2 Input- Chip enable 2 input, active HIGH. Sampled on the rising edge of CLK. Used in conjunction with CE1

synchronous and CE3 to select/deselect the device. CE2 is sampled only when a new external address is loaded.

CE3 Input- Chip enable 3 input, active LOW. Sampled on the rising edge of CLK. Used in conjunction with CE1

synchronous and CE2 to select/deselect the device. CE3 is sampled only when a new external address is loaded.

OE Input- Output enable, asynchronous input, active LOW. Controls the direction of the I/O pins. When LOW,

asynchronous the I/O pins behave as outputs. When deasserted HIGH, DQ pins are tri-stated, and act as input data

pins. OE is masked during the first clock of a read cycle when emerging from a deselected state.

ADV

Input- Advance input signal, sampled on the rising edge of CLK, active LOW. When asserted, it

synchronous automatically increments the address in a burst cycle.

ADSP

ADSC

Input- Address strobe from processor, sampled on the rising edge of CLK, active LOW. When asserted

synchronous LOW, addresses presented to the device are captured in the address registers. A1: A0 are also loaded

into the burst counter. When ADSP and ADSC are both asserted, only ADSP is recognized. ASDP is

ignored when CE1 is deasserted HIGH.

Input- Address strobe from controller, sampled on the rising edge of CLK, active LOW. When asserted

synchronous LOW, addresses presented to the device are captured in the address registers. A1:A0 are also loaded

into the burst counter. When ADSP and ADSC are both asserted, only ADSP is recognized.

ZZ Input- ZZ “sleep” input, active HIGH. When asserted HIGH places the device in a non-time-critical “sleep”

asynchronous condition with data integrity preserved. For normal operation, this pin has to be LOW or left floating. ZZ

pin has an internal pull-down.

DQs, DQPs

I/O- Bidirectional data I/O lines. As inputs, they feed into an on-chip data register that is triggered by the

synchronous rising edge of CLK. As outputs, they deliver the data contained in the memory location specified by the

addresses presented during the previous clock rise of the read cycle. The direction of the pins is

controlled by OE. When OE is asserted LOW, the pins behave as outputs. When HIGH, DQs and DQPX

are placed in a tri-state condition.

VDD

VSS

VSSQ

VDDQ

Power supply Power supply inputs to the core of the device.

Ground Ground for the core of the device.

I/O ground Ground for the I/O circuitry.

I/O power Power supply for the I/O circuitry.

supply

MODE

Input-

static

Selects burst order. When tied to GND selects linear burst sequence. When tied to VDD or left floating

selects interleaved burst sequence. This is a strap pin and should remain static during device operation.

Mode pin has an internal pull-up.

NC – No Connects. Not internally connected to the die.

Document Number: 38-05352 Rev. *N

Page 5 of 24

5 Page

CY7C1444AV33

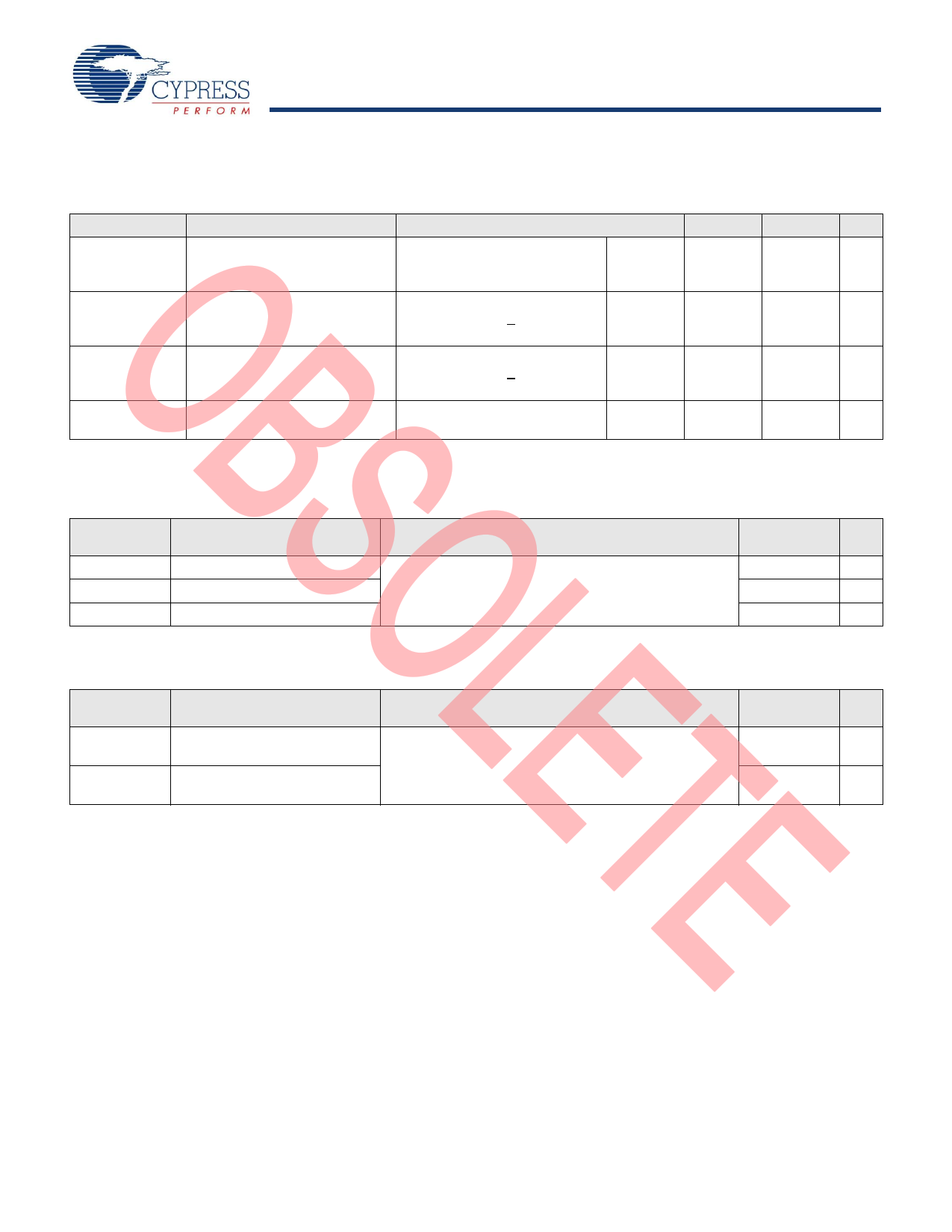

Electrical Characteristics (continued)

Over the Operating Range

Parameter [9, 10]

Description

ISB1 Automatic CE power-down

current – TTL inputs

ISB2 Automatic CE power-down

current – CMOS inputs

ISB3 Automatic CE power-down

current – CMOS inputs

ISB4 Automatic CE power-down

current – TTL inputs

Test Conditions

VDD = Max, device deselected,

VIN VIH or VIN VIL,

f = fMAX = 1/tCYC

VDD = Max, device deselected,

VIN 0.3 V or VIN > VDDQ – 0.3 V,

f=0

All speeds

All speeds

VDD = Max, device deselected, or

VIN 0.3 V or VIN > VDDQ – 0.3 V,

f = fMAX = 1/tCYC

VDD = Max, device deselected,

VIN VIH or VIN VIL, f = 0

All speeds

All speeds

Min

–

–

–

–

Max Unit

225 mA

120 mA

200 mA

135 mA

Capacitance

Parameter [11]

Description

CIN

CCLK

CI/O

Input capacitance

Clock input capacitance

Input/output capacitance

Thermal Resistance

Parameter [11]

Description

JA Thermal resistance

(junction to ambient)

JC Thermal resistance

(junction to case)

Test Conditions

TA = 25 C, f = 1 MHz,

VDD = 3.3 V, VDDQ = 2.5 V

100-pin TQFP

Max

6.5

3

5.5

Unit

pF

pF

pF

Test Conditions

100-pin TQFP

Package

Unit

Test conditions follow standard test methods and

procedures for measuring thermal impedance, per

EIA/JESD51.

25.21

2.28

C/W

C/W

Note

11. Tested initially and after any design or process change that may affect these parameters.

Document Number: 38-05352 Rev. *N

Page 11 of 24

11 Page | ||

| Páginas | Total 24 Páginas | |

| PDF Descargar | [ Datasheet CY7C1444AV33.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| CY7C1444AV33 | 36-Mbit Pipelined DCD Sync SRAM | Cypress Semiconductor |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |