|

|

PDF CY7C1386KV33 Data sheet ( Hoja de datos )

| Número de pieza | CY7C1386KV33 | |

| Descripción | 18-Mbit Pipelined DCD Sync SRAM | |

| Fabricantes | Cypress Semiconductor | |

| Logotipo | ||

Hay una vista previa y un enlace de descarga de CY7C1386KV33 (archivo pdf) en la parte inferior de esta página. Total 23 Páginas | ||

|

No Preview Available !

CY7C1386KV33

CY7C1387KV33

18-Mbit (512K × 36/1M × 18)

Pipelined DCD Sync SRAM

18-Mbit (512K × 36/1M × 18) Pipelined DCD Sync SRAM

Features

■ Supports bus operation up to 200 MHz

■ Available speed grades are 200, and 167 MHz

■ Registered inputs and outputs for pipelined operation

■ Optimal for performance (double-cycle deselect)

■ Depth expansion without wait state

■ 3.3 V core power supply (VDD)

■ 2.5 V or 3.3 V I/O power supply (VDDQ)

■ Fast clock-to-output times

❐ 3 ns (for 200 MHz device)

■ Provides high performance 3-1-1-1 access rate

■ User selectable burst counter supporting interleaved or linear

burst sequences

■ Separate processor and controller address strobes

■ Synchronous self-timed writes

■ Asynchronous output enable

■ CY7C1386KV33 available in JEDEC-standard Pb-free 100-pin

TQFP. CY7C1387KV33 available in JEDEC-standard Pb-free

100-pin TQFP

■ ZZ sleep mode option

Functional Description

The CY7C1386KV33/CY7C1387KV33 SRAM integrates

512K × 36/1M × 18 SRAM cells with advanced synchronous

peripheral circuitry and a two-bit counter for internal burst

operation. All synchronous inputs are gated by registers

controlled by a positive edge triggered clock input (CLK). The

synchronous inputs include all addresses, all data inputs,

address-pipelining chip enable (CE1), depth expansion chip

enables (CE2 and CE3), burst control inputs (ADSC, ADSP, and

ADV), write enables (BWX, and BWE), and global write (GW).

Asynchronous inputs include the output enable (OE) and the ZZ

pin.

Addresses and chip enables are registered at rising edge of

clock when either address strobe processor (ADSP) or address

strobe controller (ADSC) are active. Subsequent burst

addresses can be internally generated as controlled by the

advance pin (ADV).

Address, data inputs, and write controls are registered on-chip

to initiate a self timed write cycle.This part supports byte write

operations (see Pin Configurations on page 5 and Truth Table on

page 9 for further details). Write cycles can be one to four bytes

wide as controlled by the byte write control inputs. GW active

LOW causes all bytes to be written. This device incorporates an

additional pipelined enable register which delays turning off the

output buffers an additional cycle when a deselect is

executed.This feature allows depth expansion without penalizing

system performance.

The CY7C1386KV33/CY7C1387KV33 operates from a +3.3 V

core power supply while all outputs operate with a +3.3 V or

+2.5 V supply. All inputs and outputs are JEDEC-standard and

JESD8-5-compatible.

Selection Guide

Maximum access time

Maximum operating current

Description

200 MHz 167 MHz Unit

3.0 3.4 ns

× 18 158

× 36 178

143

mA

163

Cypress Semiconductor Corporation • 198 Champion Court

Document Number: 001-97893 Rev. *D

• San Jose, CA 95134-1709 • 408-943-2600

Revised July 1, 2016

1 page

CY7C1386KV33

CY7C1387KV33

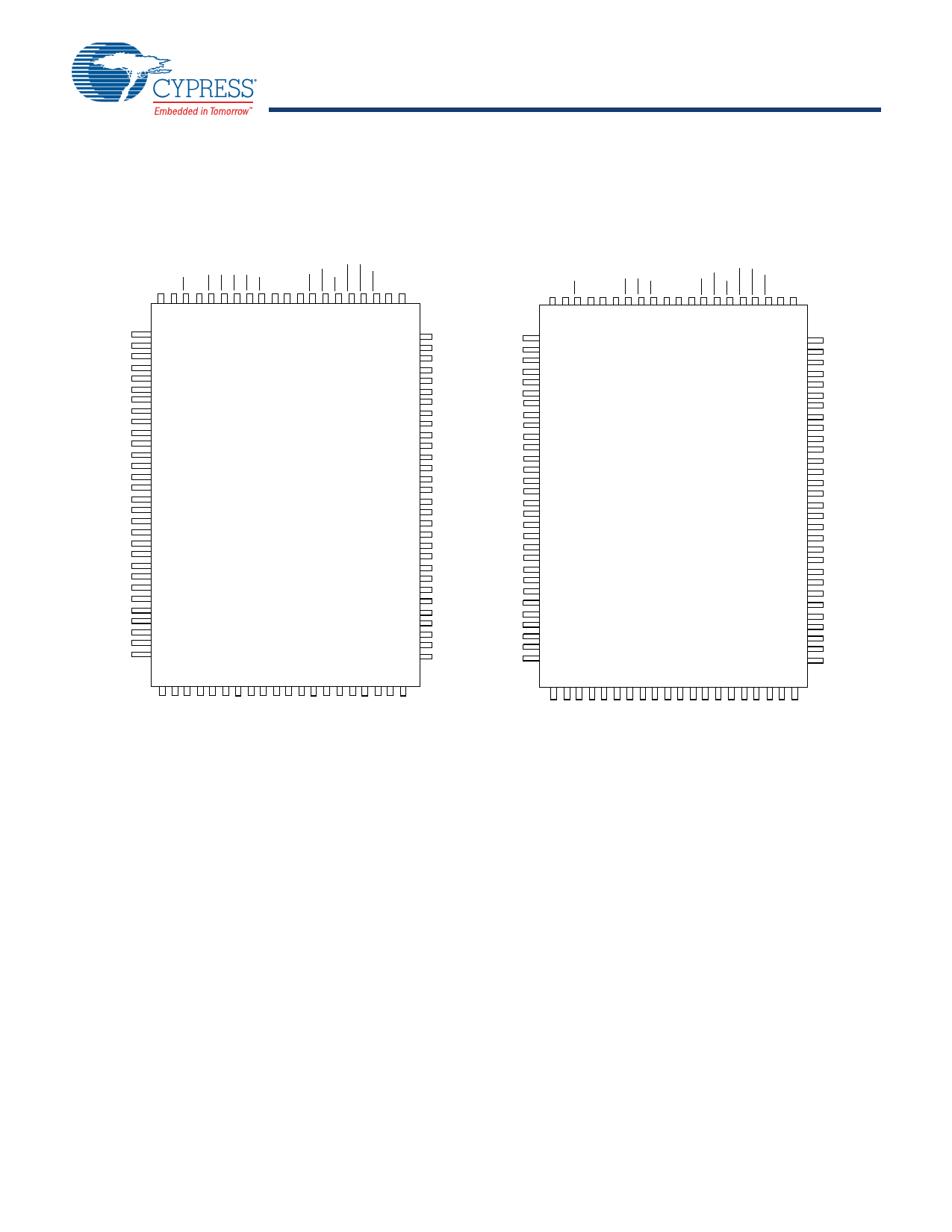

Pin Configurations

Figure 1. 100-pin TQFP (14 × 20 × 1.4 mm) pinout (3 Chip Enable)

DQPC

DQC

DQC

VDDQ

VSSQ

DQC

DQC

DQC

DQC

VSSQ

VDDQ

DQC

DQC

NC

VDD

NC

VSS

DQD

DQD

VDDQ

VSSQ

DQD

DQD

DQD

DQD

VSSQ

VDDQ

DQD

DQD

DQPD

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

CY7C1386KV33

(512K × 36)

80 DQPB

NC

79 DQB

NC

78 DQB

NC

77

VDDQ

VDDQ

76

VSSQ

VSSQ

75 DQB

NC

74 DQB

NC

73 DQB

DQB

72 DQB

DQB

71

VSSQ

VSSQ

70

VDDQ

VDDQ

69 DQB

DQB

68 DQB

DQB

67 VSS

NC

66 NC

65 VDD

VDD

NC

64 ZZ

63 DQA

VSS

DQB

62 DQA

DQB

61

VDDQ

VDDQ

60

VSSQ

VSSQ

59 DQA

DQB

58 DQA

DQB

57

DQA

DQPB

56 DQA

NC

55

VSSQ

VSSQ

54

VDDQ

VDDQ

53 DQA

NC

52 DQA

NC

51 DQPA

NC

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

CY7C1387KV33

(1M × 18)

80 A

79 NC

78 NC

77 VDDQ

76 VSSQ

75 NC

74 DQPA

73 DQA

72 DQA

71 VSSQ

70 VDDQ

69 DQA

68 DQA

67 VSS

66 NC

65 VDD

64 ZZ

63 DQA

62 DQA

61 VDDQ

60 VSSQ

59 DQA

58 DQA

57 NC

56 NC

55 VSSQ

54 VDDQ

53 NC

52 NC

51 NC

Document Number: 001-97893 Rev. *D

Page 5 of 23

5 Page

CY7C1386KV33

CY7C1387KV33

Maximum Ratings

Exceeding maximum ratings may shorten the useful life of the

device. User guidelines are not tested.

Storage temperature ................................ –65 °C to +150 °C

Ambient temperature

with power applied ................................... –55 °C to +125 °C

Supply voltage on VDD relative to GND .......–0.5 V to +4.6 V

Supply voltage on VDDQ relative to GND ...... –0.5 V to +VDD

DC voltage applied to outputs

in tristate ...........................................–0.5 V to VDDQ + 0.5 V

DC input voltage ................................. –0.5 V to VDD + 0.5 V

Current into outputs (LOW) ........................................ 20 mA

Static discharge voltage

(per MIL-STD-883, Method 3015) .......................... > 2001 V

Latch-up current .................................................... > 200 mA

Operating Range

Range

Ambient

Temperature

Commercial 0 °C to +70 °C

VDD

3.3 V– 5% /

+10%

VDDQ

2.5 V – 5% to

VDD

Neutron Soft Error Immunity

Parameter

Description

Test

Conditions

Typ

Max*

Unit

LSBU

(Device

without

ECC)

Logical

Single-Bit

Upsets

25 °C

<5 5 FIT/

Mb

LMBU

Logical

Multi-Bit

Upsets

25 °C

0 0.01 FIT/

Mb

SEL

Single Event 85 °C

0 0.1 FIT/

Latch up

Dev

* No LMBU or SEL events occurred during testing; this column represents a

statistical 2, 95% confidence limit calculation. For more details refer to Application

Note AN54908 “Accelerated Neutron SER Testing and Calculation of Terrestrial

Failure Rates”.

Electrical Characteristics

Over the Operating Range

Parameter [8, 9]

Description

Test Conditions

VDD

VDDQ

Power Supply Voltage

I/O Supply Voltage

for 3.3 V I/O

for 2.5 V I/O

VOH

Output HIGH Voltage

for 3.3 V I/O, IOH = –4.0 mA

for 2.5 V I/O, IOH = –1.0 mA

VOL

Output LOW Voltage

for 3.3 V I/O, IOL = 8.0 mA

for 2.5 V I/O, IOL = 1.0 mA

VIH

Input HIGH Voltage[8]

for 3.3 V I/O

for 2.5 V I/O

VIL

Input LOW Voltage[8]

for 3.3 V I/O

for 2.5 V I/O

IX Input Leakage Current except ZZ GND VI VDDQ

and MODE

Input Current of MODE

Input = VSS

Input = VDD

Input Current of ZZ

Input = VSS

Input = VDD

IOZ

Output Leakage Current

GND VI VDDQ, Output Disabled

Notes

8. Overshoot: VIH(AC) < VDD + 1.5 V (Pulse width less than tCYC/2), undershoot: VIL(AC) > –2 V (Pulse width less than tCYC/2).

9. TPower-up: Assumes a linear ramp from 0 V to VDD(min.) of at least 200 ms. During this time VIH < VDD and VDDQ <VDD.

Min

3.135

3.135

2.375

2.4

2.0

–

–

2.0

1.7

–0.3

–0.3

–5

–30

–

–5

–

–5

Max Unit

3.6 V

VDD

2.625

V

V

–V

–V

0.4 V

0.4 V

VDD + 0.3 V

VDD + 0.3 V

0.8

V

V

V

0.7 V

5 A

– A

5 A

– A

30 A

5 A

Document Number: 001-97893 Rev. *D

Page 11 of 23

11 Page | ||

| Páginas | Total 23 Páginas | |

| PDF Descargar | [ Datasheet CY7C1386KV33.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| CY7C1386KV33 | 18-Mbit Pipelined DCD Sync SRAM | Cypress Semiconductor |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |