|

|

PDF CY7C1440KVE33 Data sheet ( Hoja de datos )

| Número de pieza | CY7C1440KVE33 | |

| Descripción | 36-Mbit Pipelined Sync SRAM | |

| Fabricantes | Cypress Semiconductor | |

| Logotipo | ||

Hay una vista previa y un enlace de descarga de CY7C1440KVE33 (archivo pdf) en la parte inferior de esta página. Total 30 Páginas | ||

|

No Preview Available !

CY7C1440KV33

CY7C1442KV33

CY7C1440KVE33

36-Mbit (1M × 36/2M × 18)

Pipelined Sync SRAM (With ECC)

36-Mbit (1M × 36/2M × 18) Pipelined Sync SRAM (With ECC)

Features

■ Supports bus operation up to 250 MHz

■ Available speed grades are 250 MHz and 167 MHz

■ Registered inputs and outputs for pipelined operation

■ 3.3 V core power supply

■ 2.5 V or 3.3 V I/O power supply

■ Fast clock-to-output time

❐ 2.5 ns (for 250 MHz device)

■ Provide high-performance 3-1-1-1 access rate

■ User-selectable burst counter supporting interleaved or linear

burst sequences

■ Separate processor and controller address strobes

■ Synchronous self-timed writes

■ Asynchronous output enable

■ Single cycle chip deselect

■ CY7C1440KV33, CY7C1442KV33 and CY7C1440KVE33 are

available in Pb-free 100-pin TQFP, and Pb-free and non Pb-free

165-ball FBGA packages.

■ IEEE 1149.1 JTAG-compatible boundary scan

■ “ZZ” sleep mode option

■ On-Chip error correction code (ECC) to reduce soft error rate

(SER)

Functional Description

The CY7C1440KV33/CY7C1442KV33/CY7C1440KVE33 SRAM

integrate 1M × 36/2M × 18/1M × 36 SRAM cells with advanced

synchronous peripheral circuitry and a two-bit counter for

internal burst operation. All synchronous inputs are gated by

registers controlled by a positive-edge-triggered clock input

(CLK). The synchronous inputs include all addresses, all data

inputs, address-pipelining chip enable (CE1), depth-expansion

chip enables (CE2 and CE3), burst control inputs (ADSC, ADSP,

and ADV), write enables (BWX and BWE), and global write (GW).

Asynchronous inputs include the output enable (OE) and the ZZ

pin.

Addresses and chip enables are registered at rising edge of

clock when either address strobe processor (ADSP) or address

strobe controller (ADSC) are active. Subsequent burst

addresses can be internally generated as controlled by the

advance pin (ADV).

Address, data inputs, and write controls are registered on-chip

to initiate a self-timed write cycle. This part supports byte write

operations (see pin descriptions and truth table for further

details). Write cycles can be one, two or four bytes wide as

controlled by the byte write control inputs. GW when active LOW

causes all bytes to be written.

The CY7C1440KV33/CY7C1442KV33/CY7C1440KVE33

operate from a +3.3 V core power supply while all outputs may

operate with either a +2.5 V or +3.3 V supply. All inputs and

outputs are JEDEC-standard JESD8-5-compatible.

Selection Guide

Maximum access time

Maximum operating current

Description

250 MHz 167 MHz Unit

2.5 3.4 ns

× 18 220 Not Offered mA

× 36 240

190

Cypress Semiconductor Corporation • 198 Champion Court

Document Number: 001-66676 Rev. *G

• San Jose, CA 95134-1709 • 408-943-2600

Revised July 5, 2016

1 page

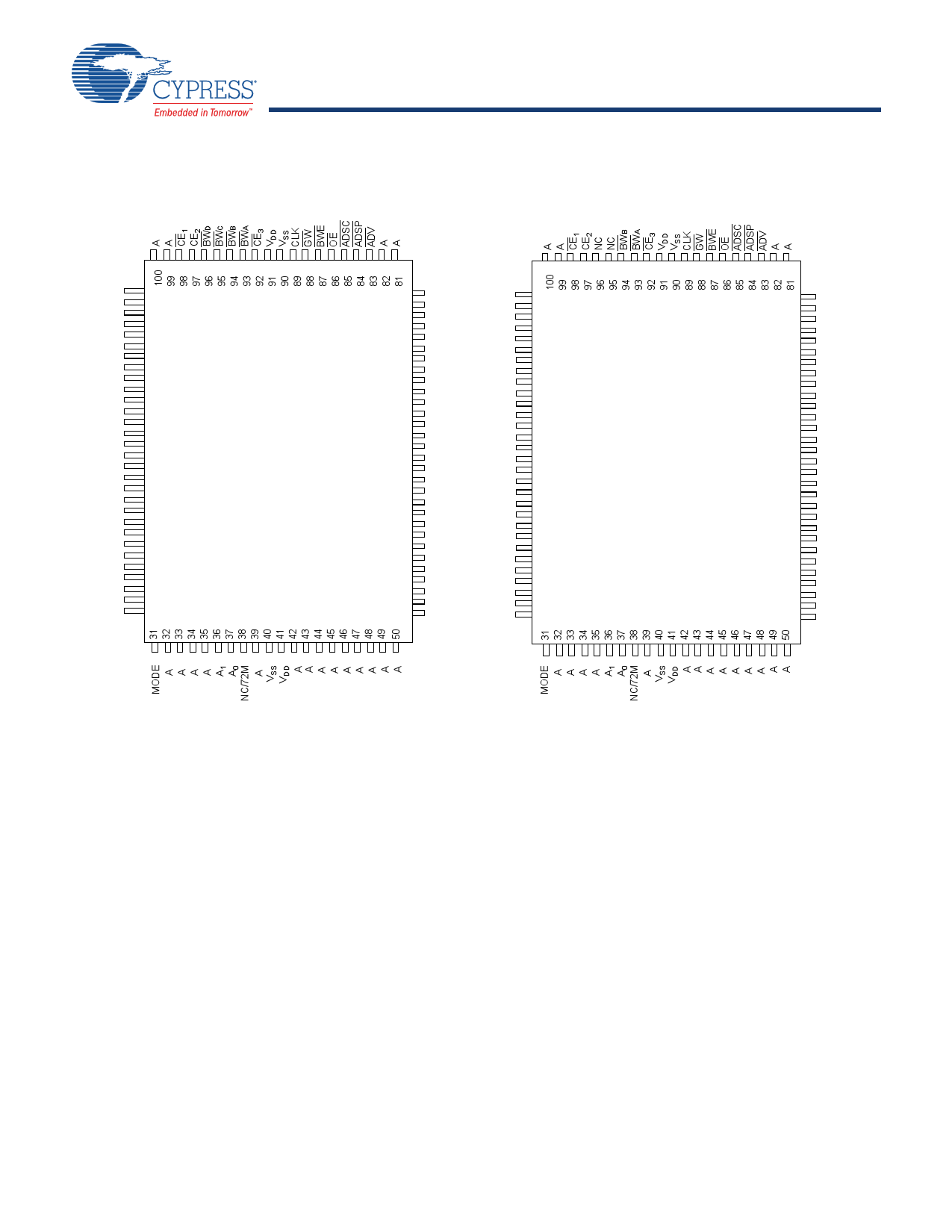

Pin Configurations

Figure 1. 100-pin TQFP Pinout

CY7C1440KV33

CY7C1442KV33

CY7C1440KVE33

DQPC

DQC

DQc

VDDQ

VSSQ

DQC

DQC

DQC

DQC

VSSQ

VDDQ

DQC

DQC

NC

VDD

NC

VSS

DQD

DQD

VDDQ

VSSQ

DQD

DQD

DQD

DQD

VSSQ

VDDQ

DQD

DQD

DQPD

1 80

2 79

3 78

4 77

5 76

6 75

7 74

8 73

9 72

10 71

11 70

12 69

13 68

14 67

15

16

17

CY7C1440KV33/CY7C1440KVE33

(1M × 36)

66

65

64

18 63

19 62

20 61

21 60

22 59

23 58

24 57

25 56

26 55

27 54

28 53

29 52

30 51

DQPB

DQB

DQB

VDDQ

VSSQ

DQB

DQB

DQB

DQB

VSSQ

VDDQ

DQB

DQB

VSS

NC

VDD

ZZ

DQA

DQA

VDDQ

VSSQ

DQA

DQA

DQA

DQA

VSSQ

VDDQ

DQA

DQA

DQPA

NC

NC

NC

VDDQ

VSSQ

NC

NC

DQB

DQB

VSSQ

VDDQ

DQB

DQB

NC

VDD

NC

VSS

DQB

DQB

VDDQ

VSSQ

DQB

DQB

DQPB

NC

VSSQ

VDDQ

NC

NC

NC

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

CY7C1442KV33

(2M × 18)

80 A

79 NC

78 NC

77 VDDQ

76 VSSQ

75 NC

74 DQPA

73 DQA

72 DQA

71 VSSQ

70 VDDQ

69 DQA

68 DQA

67 VSS

66 NC

65 VDD

64 ZZ

63 DQA

62 DQA

61 VDDQ

60 VSSQ

59 DQA

58 DQA

57 NC

56 NC

55 VSSQ

54 VDDQ

53 NC

52 NC

51 NC

Document Number: 001-66676 Rev. *G

Page 5 of 33

5 Page

CY7C1440KV33

CY7C1442KV33

CY7C1440KVE33

Truth Table

The truth table for CY7C1440KV33/CY7C1442KV33/CY7C1440KVE33 is as follows [2, 3, 4, 5, 6, 7].

Operation

Add. Used CE1 CE2 CE3 ZZ ADSP ADSC ADV WRITE OE

Deselect cycle, power-down

None

HXX L

X

LXXX

Deselect cycle, power-down

None

LLXL

L

XXXX

Deselect cycle, power-down

None

L XH L

L

XXXX

Deselect cycle, power-down

None

LLXL

H

LXXX

Deselect cycle, power-down

None

L XH L

H

LXXX

Sleep mode, power-down

None

XXXH

X

XXXX

READ cycle, begin burst

External L H L L

L

XXX L

READ cycle, begin burst

External L H L L

L

XXXH

WRITE cycle, begin burst

External L H L L

H

LXL

X

READ cycle, begin burst

External L H L L

H

L XH L

READ cycle, begin burst

External L H L L

H

L XHH

READ cycle, continue burst

Next

XXX L

H

HLHL

READ cycle, continue burst

Next

XXX L

H

HLHH

READ cycle, continue burst

Next

HXX L

X

HLHL

READ cycle, continue burst

Next

HXX L

X

HLHH

WRITE cycle, continue burst

Next

XXX L

H

HL

L

X

WRITE cycle, continue burst

Next

HXX L

X

HL

L

X

READ cycle, suspend burst Current X X X L

H

HHH L

READ cycle, suspend burst Current X X X L

H

HHHH

READ cycle, suspend burst Current H X X L

X

HHH L

READ cycle, suspend burst Current H X X L

X

HHHH

WRITE cycle, suspend burst Current X X X L

H

HH L

X

WRITE cycle, suspend burst Current H X X L

X

HH L

X

CLK

L–H

L–H

L–H

L–H

L–H

X

L–H

L–H

L–H

L–H

L–H

L–H

L–H

L–H

L–H

L–H

L–H

L–H

L–H

L–H

L–H

L–H

L–H

DQ

Tri-state

Tri-state

Tri-state

Tri-state

Tri-state

Tri-state

Q

Tri-state

D

Q

Tri-state

Q

Tri-state

Q

Tri-state

D

D

Q

Tri-state

Q

Tri-state

D

D

Notes

2. X = “Don't Care.” H = Logic HIGH, L = Logic LOW.

3. WRITE = L when any one or more byte write enable signals and BWE = L or GW = L. WRITE = H when all byte write enable signals, BWE, GW = H.

4. The DQ pins are controlled by the current cycle and the OE signal. OE is asynchronous and is not sampled with the clock.

5. CE1, CE2, and CE3 are available only in the TQFP package. BGA package has only 2 chip selects CE1 and CE2.

6.

The SRAM always initiates a read cycle when

the ADSP or with the assertion of ADSC. As a

ADSP

result,

is asserted,

OE must be

rdergivaerndlHesIGs HofpthrieorsttoatteheofsGtaWrt ,oBf tWheEw, orirteBcWycXl.eWtoritaelslomw athyeoocucutpruotsnltyootrni-ssutabtsee. qOuEenist

clocks

a don't

after

care

for the remainder of the write cycle.

7. OE is asynchronous and is not sampled with the clock rise. It is masked internally during write cycles. During a read cycle all data bits are tri-state when OE is

inactive or when the device is deselected, and all data bits behave as output when OE is active (LOW).

Document Number: 001-66676 Rev. *G

Page 11 of 33

11 Page | ||

| Páginas | Total 30 Páginas | |

| PDF Descargar | [ Datasheet CY7C1440KVE33.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| CY7C1440KVE33 | 36-Mbit Pipelined Sync SRAM | Cypress Semiconductor |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |