|

|

PDF GM72V66841CLT Data sheet ( Hoja de datos )

| Número de pieza | GM72V66841CLT | |

| Descripción | 2M x 8-Bit x 4 Bank SDRAM | |

| Fabricantes | LG Semicon | |

| Logotipo | ||

Hay una vista previa y un enlace de descarga de GM72V66841CLT (archivo pdf) en la parte inferior de esta página. Total 30 Páginas | ||

|

No Preview Available !

LG Semicon Co.,Ltd.

Description

The GM72V66841CT/CLT is a synchronous

dynamic random access memory comprised of

67,108,864 memory cells and logic including

input and output circuits operating synchronously

by referring to the positive edge of the externally

provided Clock.

The GM72V66841CT/CLT provides four

banks of 2,097,152 word by 8 bit to realize high

bandwidth with the Clock frequency up to 125

Mhz.

Features

* PC100,PC66 Compatible

7K(2-2-2), 7J(3-2-2), 10K(PC66)

* 3.3V single Power supply

* LVTTL interface

* Max Clock frequency

100/125 MHz

* 4,096 refresh cycle per 64 ms

* Two kinds of refresh operation

Auto refresh/ Self refresh

* Programmable burst access capability ;

- Sequence:Sequential / Interleave

- Length :1/2/4/8/FP

* Programmable CAS latency : 2/3

* 4 Banks can operate independently or

simultaneously

* Burst read/burst write or burst read/single

write operation capability

* Input and output masking by DQM input

* One Clock of back to back read or write

command interval

* Synchronous Power down and Clock

suspend capability with one Clock latency

for both entry and exit

*JEDEC Standard 54Pin 400mil TSOP II

Package

GM72V66841CT/CLT

2,097,152 WORD x 8 BIT x 4 BANK

SYNCHRONOUS DYNAMIC RAM

Pin Configuration

VCC

DQ0

VCCQ

NC

DQ1

VSSQ

NC

DQ2

VCCQ

NC

DQ3

VSSQ

NC

VCC

NC

/WE

/CAS

/RAS

/CS

BA0/A13

BA1/A12

A10,AP

A0

A1

A2

A3

VCC

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

JEDEC STANDARD

400 mil 54 PIN TSOP II

(TOP VIEW)

54 VSS

53 DQ7

52 VSSQ

51 NC

50 DQ6

49 VCCQ

48 NC

47 DQ5

46 VSSQ

45 NC

44 DQ4

43 VCCQ

42 NC

41 VSS

40 NC

39 DQM

38 CLK

37 CKE

36 NC

35 A11

34 A9

33 A8

32 A7

31 A6

30 A5

29 A4

28 VSS

Pin Name

CLK

CKE

CS

RAS

CAS

WE

A0~A9,A11

A10 / AP

BA0/A13

~BA1/A12

DQ0~DQ7

DQM

VCCQ

VSSQ

VCC

VSS

NC

Clock

Clock Enable

Chip Select

Row Address Strobe

Column Address Strobe

Write Enable

Address input

Address input or Auto Precharge

Bank select

Data input / Data output

Data input / output Mask

VCC for DQ

VSS for DQ

Power for internal circuit

Ground for internal circuit

No Connection

1

1 page

LG Semicon

Ignore command [DESL]: When this command

is set (CS is High), the synchronous DRAM

ignores command input at the Clock. However,

the internal status is held.

No operation [NOP]: This command is not an

execution command. However, the internal

operations continue.

Burst stop in full page [BST] : This

command stops a full-page burst operation (burst

length = full-page(512;GM72V66841CT/CLT)

and is illegal otherwise. Full page burst continues

until this command is input. When data

input/output is completed for full-page of data, it

automatically returns to the start address, and

input/output is performed repeatedly.

Column address strobe and read command

[READ]: This command starts a read operation.

In addition, the start address of burst read is

determined by the column address

AY0 to AY8; GM72V66841CT/CLT) and the

bank select address (A12/A13). After the read

operation, the output buffer becomes High-Z.

Read with auto-Precharge [READ A]: This

command automatically performs a Precharge

operation after a burst read with a burst length of

1, 2, 4 or 8. When the burst length is full-page,

this command is illegal.

Column address strobe and write command

[WRIT]: This command starts a write operation.

When the burst write mode is selected, the column

address (AY0 to AY8; GM72V66841CT/CLT)

and the bank select address (A12/A13) become the

burst write start address. When the single write

mode is selected, data is only written to the

location specified by the column address (AY0 to

AY8;GM72V66841CT/CLT) and the bank select

address (A12/A13).

GM72V66841CT/CLT

Write with auto-Precharge [WRIT A]: This

command automatically performs a Precharge

operation after a burst write with a length of 1, 2,

4 or 8, or after a single write operation. When the

burst length is full-page, this command is illegal.

Row address strobe and bank activate

[ACTV]: This command activates the bank that

is selected by A12/A13(BS) and determines the

row address (AX0 to AX11). If A12 is Low and

if A13 is Low, bank 0 is activated. If A12 is High

and A13 is Low, bank 1 is activated. If A12 is

Low and A13 is High, bank 2 is activated. If A12

is High and A13 is High, bank 3 is activated.

Precharge selected bank [PRE]: This

command starts Precharge operation for the bank

selected by A12/A13. If A12 is Low and if A13 is

Low, bank 0 is selected. If A12 is High and A13

is Low, bank 1 is selected. If A12 is Low and

A13 is High, bank 2 is selected. If A12 is High

and A13 is High, bank 3 is selected.

Precharge all banks [PALL]: This command

starts a Precharge operation for all banks.

Refresh [REF/SELF]: This command starts the

refresh operation. There are two types of refresh

operation, the one is auto-refresh, and the other is

self-refresh. For details, refer to the CKE truth

table section.

Mode register set [MRS]: Synchronous DRAM

has a mode register that defines how it operates.

The mode register is specified by the address pins

(A0 to A11) at the mode register set cycle. For

details, refer to the mode register configuration.

After Power on, the contents of the mode register

are undefined, execute the mode register set

command to set up the mode register.

5

5 Page

LG Semicon

GM72V66841CT/CLT

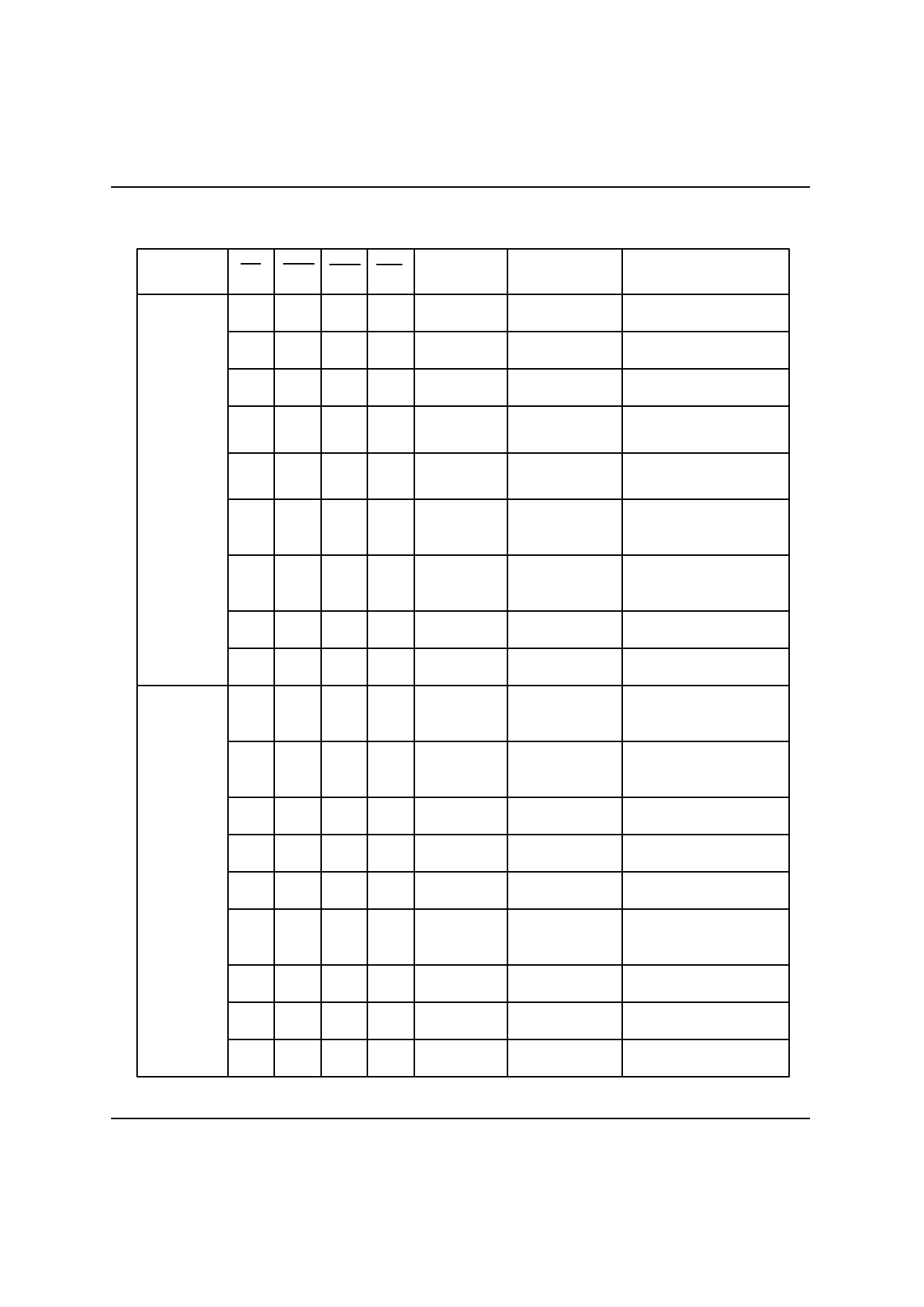

Function Truth Table (Continued)

Current

state

Write

CS RAS CAS WE Address

Command

Operation

H X X XX

DESL

Continue burst to end

L H H HX

NOP

Continue burst to end

L H H LX

BST

Burst stop on full page

L H L H BA, CA, A10 READ/READ A Term burst and New

read

L H L L BA, CA, A10 WRIT/WRIT A Term burst and New

write

L L H H BA, RA

ACTV

Other bank active

*3

ILLEGAL on same bank

L L H L BA, A10 PRE, PALL Term burst write and

Precharge*2

L L L HX

REF, SELF

ILLEGAL

L L L L MODE

MRS

ILLEGAL

Write with H X X X X

auto-

Precharge

L H H HX

DESL

NOP

Continue burst to end

and Precharge

Continue burst to end

and Precharge

L H H LX

BST

ILLEGAL

L H L H BA, CA, A10 READ/READ A ILLEGAL

L H L L BA, CA, A10 WRIT/WRIT A ILLEGAL

L L H H BA, RA

ACTV

Other bank active *3

ILLEGAL on same bank

L L H L BA, A10 PRE, PALL ILLEGAL

L L L HX

REF, SELF

ILLEGAL

L L L L MODE

MRS

ILLEGAL

11

11 Page | ||

| Páginas | Total 30 Páginas | |

| PDF Descargar | [ Datasheet GM72V66841CLT.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| GM72V66841CLT | 2M x 8-Bit x 4 Bank SDRAM | LG Semicon |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |