|

|

PDF S25FL127S Data sheet ( Hoja de datos )

| Número de pieza | S25FL127S | |

| Descripción | 128 Mbit (16 Mbyte) 3.0V SPI Flash Memory | |

| Fabricantes | Cypress Semiconductor | |

| Logotipo | ||

Hay una vista previa y un enlace de descarga de S25FL127S (archivo pdf) en la parte inferior de esta página. Total 30 Páginas | ||

|

No Preview Available !

S25FL127S

128 Mbit (16 Mbyte)

3.0V SPI Flash Memory

Features

CMOS 3.0 Volt Core

Density

– 128 Mbits (16 Mbytes)

Serial Peripheral Interface (SPI) with Multi-I/O

– SPI Clock polarity and phase modes 0 and 3

– Extended Addressing: 24- or 32-bit address options

– Serial Command set and footprint compatible with S25FL-A,

S25FL-K, and S25FL-P SPI families

– Multi I/O Command set and footprint compatible with

S25FL-P SPI family

READ Commands

– Normal, Fast, Dual, Quad

– AutoBoot - power up or reset and execute a Normal or Quad read

command automatically at a preselected address

– Common Flash Interface (CFI) data for configuration information.

Programming (0.8 Mbytes/s)

– 256- or 512-byte Page Programming buffer options

– Quad-Input Page Programming (QPP) for slow clock systems

Erase (0.5 Mbytes/s)

– Hybrid sector size option - physical set of sixteen 4-kbyte sectors

at top or bottom of address space with all remaining sectors of

64 kbytes

– Uniform sector option - always erase 256-kbyte blocks for software

compatibility with higher density and future devices.

Performance Summary

Cycling Endurance

– 100,000 Program-Erase Cycles per sector minimum

Data Retention

– 20 Year Data Retention typical

Security features

– One Time Program (OTP) array of 1024 bytes

– Block Protection:

– Status Register bits to control protection against program or erase

of a contiguous range of sectors.

– Hardware and software control options

– Advanced Sector Protection (ASP)

– Individual sector protection controlled by boot code or password

Cypress® 65 nm MirrorBit Technology with Eclipse™ Architecture

Supply Voltage: 2.7V to 3.6V

Temperature Range:

– Industrial (-40°C to +85°C)

– Industrial Plus (-40°C to +105°C)

Packages (all Pb-free)

– 8-lead SOIC (208 mil)

– 16-lead SOIC (300 mil)

– 8-contact WSON 6 x 5 mm

– BGA-24 6 x 8 mm

– 5 x 5 ball (FAB024) and 4 x 6 ball (FAC024) footprint options

– Known Good Die and Known Tested Die

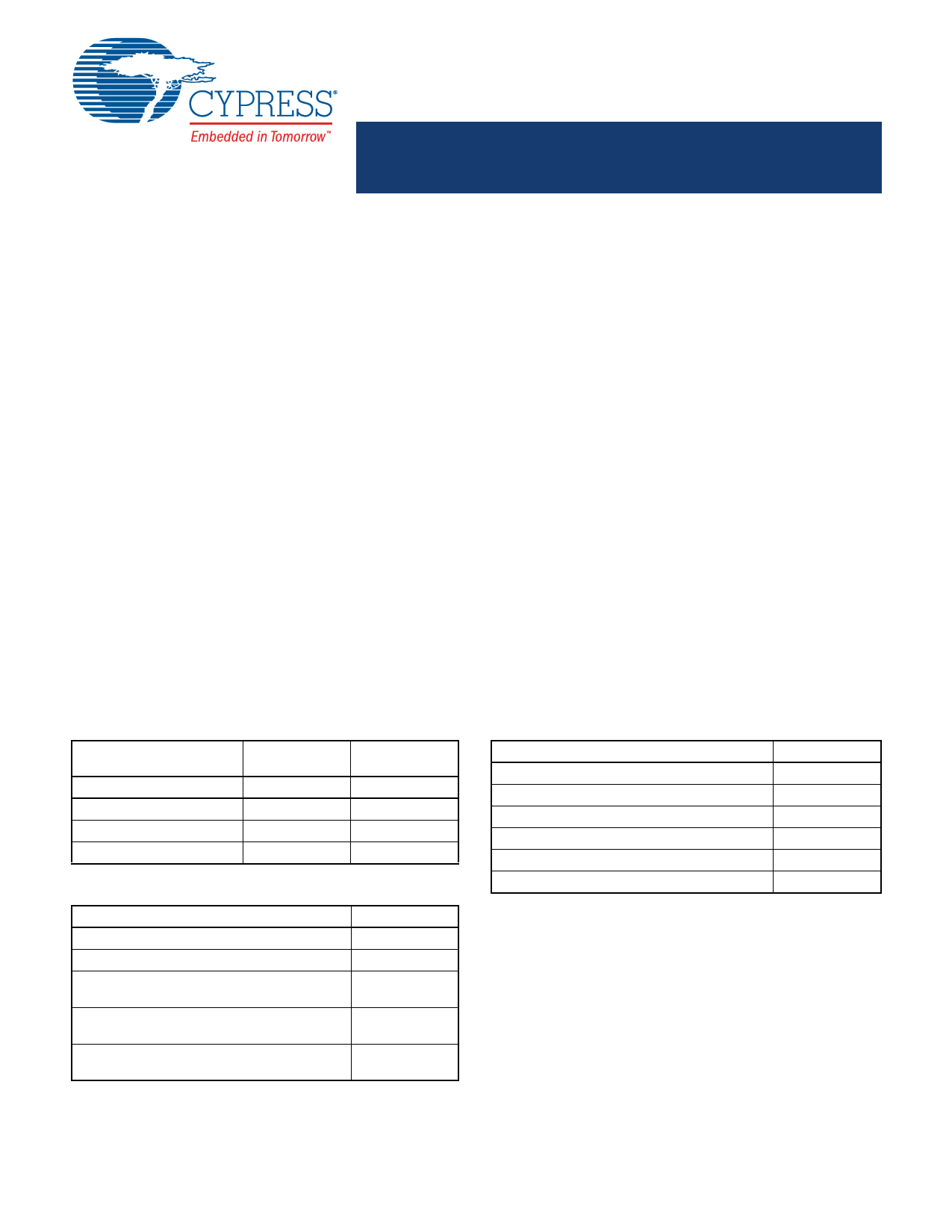

Maximum Read Rates

Command

Read

Fast Read

Dual Read

Quad Read

Clock Rate

(MHz)

50

108

108

108

Mbytes/s

6.25

13.5

27

54

Typical Program and Erase Rates

Operation

Page Programming (256-byte page buffer)

Page Programming (512-byte page buffer)

4-kbyte Physical Sector Erase (Hybrid Sector

Option)

64-kbyte Physical Sector Erase (Hybrid Sector

Option)

256-kbyte Logical Sector Erase (Uniform Sector

Option)

kbytes/s

650

800

30

500

500

Current Consumption

Operation

Serial Read 50 MHz

Serial Read 108 MHz

Quad Read 108 MHz

Program

Erase

Standby

Current (mA)

16 (max)

24 (max)

47 (max)

50 (max)

50 (max)

0.07 (typ)

Cypress Semiconductor Corporation • 198 Champion Court

Document Number: 001-98282 Rev. *G

• San Jose, CA 95134-1709 • 408-943-2600

Revised July 13, 2016

1 page

S25FL127S

1.2.2

Known Differences from Prior Generations

1.2.2.1

Error Reporting

Prior generation FL memories either do not have error status bits or do not set them if program or erase is attempted on a protected

sector. The FL-S family does have error reporting status bits for program and erase operations. These can be set when there is an

internal failure to program or erase or when there is an attempt to program or erase a protected sector. In either case the program or

erase operation did not complete as requested by the command.

1.2.2.2

Secure Silicon Region (OTP)

The size and format (address map) of the One Time Program area is different from prior generations. The method for protecting

each portion of the OTP area is different. For additional details see Secure Silicon Region (OTP) on page 59.

1.2.2.3

Configuration Register Freeze Bit

The configuration register Freeze bit CR1[0], locks the state of the Block Protection bits as in prior generations. In the FL-S family it

also locks the state of the configuration register TBPARM bit CR1[2], TBPROT bit CR1[5], and the Secure Silicon Region (OTP)

area.

1.2.2.4

Sector Architecture

The FL127S has sixteen 4-kbyte sectors that may be located at the top or bottom of address space. Other members of the FL-S

Family and FL-P Family have thirty two 4-kbyte sectors that may be located at the top or bottom of address space.

These smaller parameter sectors may also be removed, leaving all sectors uniform in size, depending on the selected configuration

(SR2[7]).

1.2.2.5

Sector Erase Commands

The command for erasing an 8-kbyte area (two 4-kbyte sectors) is not supported.

The command for erasing a 4-kbyte sector is supported only for use on the 4-kbyte parameter sectors at the top or bottom of the

device address space. The 4-kbyte erase command will only erase the parameter sectors.

The erase command for 64-kbyte sectors is supported when the configuration option for 4-kbyte parameter sectors with 64-kbyte

uniform sectors is used. The 64-kbyte erase command may be applied to erase a group of sixteen 4-kbyte sectors.

The erase command for a 256-kbyte sector replaces the 64-kbyte erase command when the configuration option for 256-kbyte

uniform sectors is used.

1.2.2.6

Deep Power Down

The Deep Power Down (DPD) function is not supported in FL-S family devices.

The legacy DPD (B9h) command code is instead used to enable legacy SPI memory controllers, that can issue the former DPD

command, to access a new bank address register. The bank address register allows SPI memory controllers that do not support

more than 24 bits of address, the ability to provide higher order address bits for commands, as needed to access the larger address

space of the 256-Mbit and 512-Mbit density FL-S devices. For additional information see Extended Address on page 48.

1.2.2.7

Hardware Reset

A separate hardware reset input is provided in packages with greater than 8 connections. In 8-connection packages, a new option is

provided to replace the HOLD# / IO3 input with an IO3 / RESET# input to allow for hardware reset in small packages.

Document Number: 001-98282 Rev. *G

Page 6 of 129

5 Page

S25FL127S

When Quad I/O mode is in use, CR1[1]=1, and the device is selected with CS# low, the IO3 / RESET# is used only as IO3 for

information transfer. When CS# is high, the IO3 / RESET# is not in use for information transfer and is used as the RESET# input. By

conditioning the reset operation on CS# high during Quad mode, the reset function remains available during Quad mode.

When the system enters a reset condition, the CS# signal must be driven high as part of the reset process and the IO3 / RESET#

signal is driven low. When CS# goes high the IO3 / RESET# input transitions from being IO3 to being the RESET# input. The reset

condition is then detected when CS# remains high and the IO3 / RESET# signal remains low for tRP.

The HOLD#/IO3 or IO3/RESET# signals have an internal pull-up resistor and may be left unconnected in the host system if not used

for Quad mode or the reset function.

When Quad mode is enabled, IO3 / RESET# is ignored for tCS following CS# going high. This allows some time for the memory or

host system to actively drive IO3 / RESET# to a valid level following the end of a transfer. Following the end of a Quad I/O read the

memory will actively drive IO3 high before disabling the output during tDIS. Following a transfer in which IO3 was used to transfer

data to the memory, e.g. the QPP command, the host system is responsible for driving IO3 high before disabling the host IO3 output.

This will ensure that IO3 / Reset is not left floating or being pulled slowly to high by the internal or an external passive pull-up. Thus,

an unintended reset is not triggered by the IO3 / RESET# not being recognized as high before the end of tRP. Once IO3 / RESET# is

high the memory or host system can stop driving the signal. The integrated pull-up on IO3 will then hold IO3 high unless the host

system actively drives IO3 / RESET# to initiate a reset.

Note that IO3 / Reset# cannot be shared by more than one SPI-MIO memory if any of them are operating in Quad I/O mode as IO3

being driven to or from one selected memory may look like a reset signal to a second not selected memory sharing the same IO3 /

RESET# signal. See Section 5.3.3 IO3 / RESET# Input Initiated Hardware (Warm) Reset on page 33 for the IO3 / RESET timing.

Figure 2.1 HOLD Mode Operation

CS#

SCLK

HOLD#

SI_or_IO_(during_input)

SO_or_IO_(internal)

SO_or_IO_(external)

Valid Input

A

A

Hold Condition

Standard Use

Don't Care

B

B

Valid Input

C

BC

Hold Condition

Non-standard Use

Don't Care

D

Valid Input

D

E

E

2.10 Voltage Supply (VCC)

VCC is the voltage source for all device internal logic. It is the single voltage used for all device internal functions including read,

program, and erase. The voltage may vary from 2.7V to 3.6V.

2.11 Supply and Signal Ground (VSS)

VSS is the common voltage drain and ground reference for the device core, input signal receivers, and output drivers.

2.12 Not Connected (NC)

No device internal signal is connected to the package connector nor is there any future plan to use the connector for a signal. The

connection may safely be used for routing space for a signal on a Printed Circuit Board (PCB). However, any signal connected to an

NC must not have voltage levels higher than VCC.

2.13 Reserved for Future Use (RFU)

No device internal signal is currently connected to the package connector but is there potential future use of the connector. It is

recommended to not use RFU connectors for PCB routing channels so that the PCB may take advantage of future enhanced

features in compatible footprint devices.

Document Number: 001-98282 Rev. *G

Page 12 of 129

11 Page | ||

| Páginas | Total 30 Páginas | |

| PDF Descargar | [ Datasheet S25FL127S.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| S25FL127S | 128 Mbit (16 Mbyte) 3.0V SPI Flash Memory | Cypress Semiconductor |

| S25FL127S | 128 Mbit (16 Mbyte) MirrorBit Flash Non-Volatile Memory | SPANSION |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |