No Preview Available !

2N5415 – 2N5416

Compliant

PNP Silicon Low-Power Transistor

Qualified per MIL-PRF-19500/485

Qualified Levels:

JAN, JANTX, JANTXV

and JANS

DESCRIPTION

This family of 2N5415 and 2N5416 epitaxial planar transistors are military qualified up to a

JANS level for high-reliability applications. These devices are also available in TO-39 and low

profile U4 and UA packaging.

Important: For the latest information, visit our website http://www.microsemi.com.

FEATURES

• JEDEC registered 2N5415 through 2N5416 series

• JAN, JANTX, JANTXV, and JANS qualifications are available per MIL-PRF-19500/485.

(See part nomenclature for all available options.)

• RoHS compliant

APPLICATIONS / BENEFITS

• General purpose transistors for low power applications requiring high frequency switching.

• Low package profile

• Military and other high-reliability applications

MAXIMUM RATINGS @ TA = +25 ºC unless otherwise noted

Parameters / Test Conditions

Collector-Emitter Voltage

Collector-Base Voltage

Emitter-Base Voltage

Collector Current

Operating & Storage Junction Temperature Range

Thermal Resistance Junction-to-Ambient

Thermal Resistance Junction-to-Case

Total Power Dissipation

@ TA = +25 °C (1)

@ TC = +25 °C (2)

Symbol

V CEO

V CBO

V EBO

IC

TJ, Tstg

R ӨJA

R ӨJC

PT

2N5415 2N5416

200 300

200 350

6.0 6.0

1.0 1.0

-65 to +200

234

17.5

0.75

10

Unit

V

V

V

A

°C

oC/W

oC/W

W

Notes: 1. Derate linearly 4.29 mW/°C for TA > +25 °C

2. Derate linearly 57.2 mW/°C for TC > +25 °C

TO-5 Package

Also available in:

TO-205AD (TO-39)

package

(short-leaded)

2N5415S – 2N5416S

U4 package

(surface mount)

2N5415U4 – 2N5416U4

UA package

(surface mount)

2N5415UA – 2N5416UA

MSC – Lawrence

6 Lake Street,

Lawrence, MA 01841

Tel: 1-800-446-1158 or

(978) 620-2600

Fax: (978) 689-0803

MSC – Ireland

Gort Road Business Park,

Ennis, Co. Clare, Ireland

Tel: +353 (0) 65 6840044

Fax: +353 (0) 65 6822298

Website:

www.microsemi.com

T4-LDS-0305, Rev. 1 (7/30/13)

©2013 Microsemi Corporation

Page 1 of 6

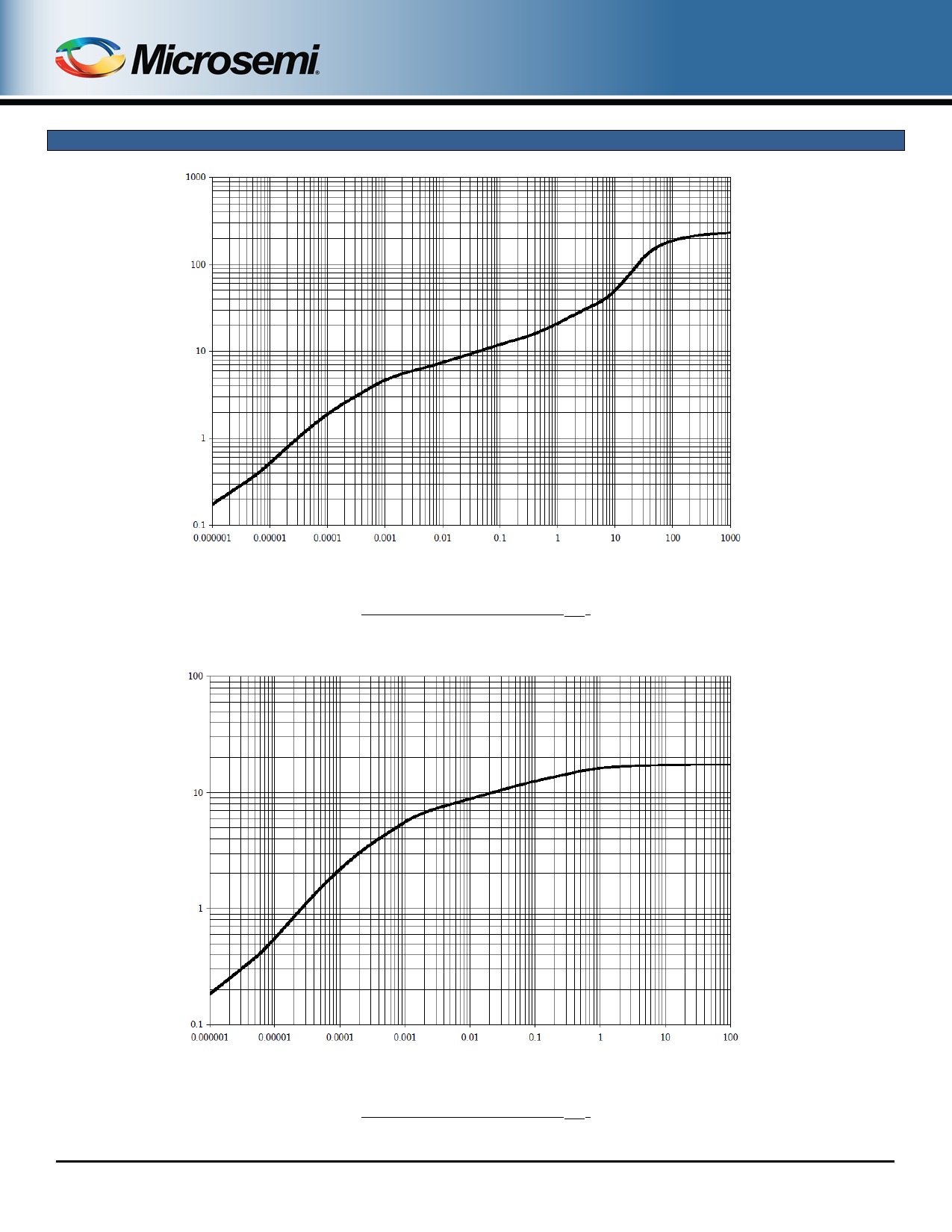

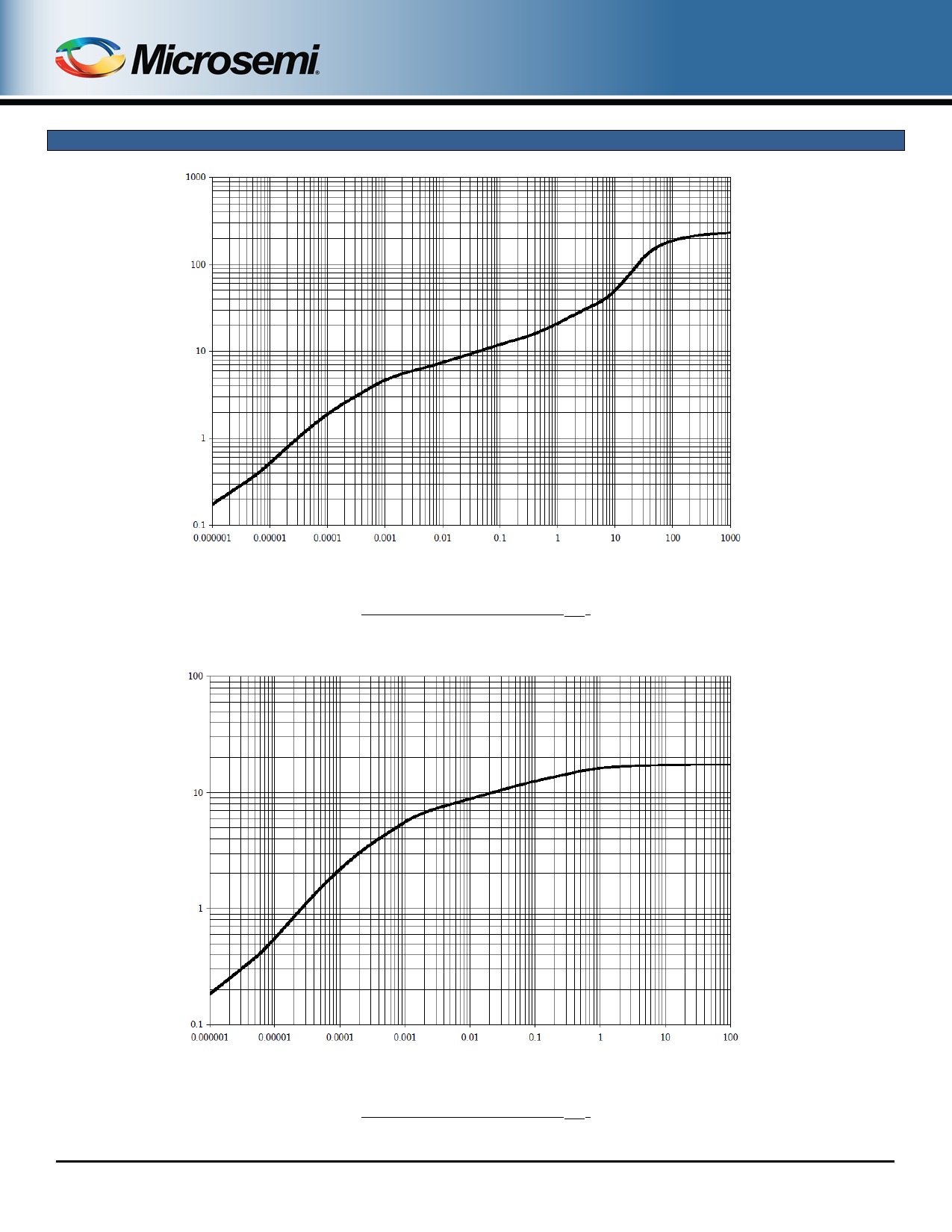

GRAPHS

2N5415 – 2N5416

Time (s)

FIGURE 1

Thermal impedance graph (RӨJA)

T4-LDS-0305, Rev. 1 (7/30/13)

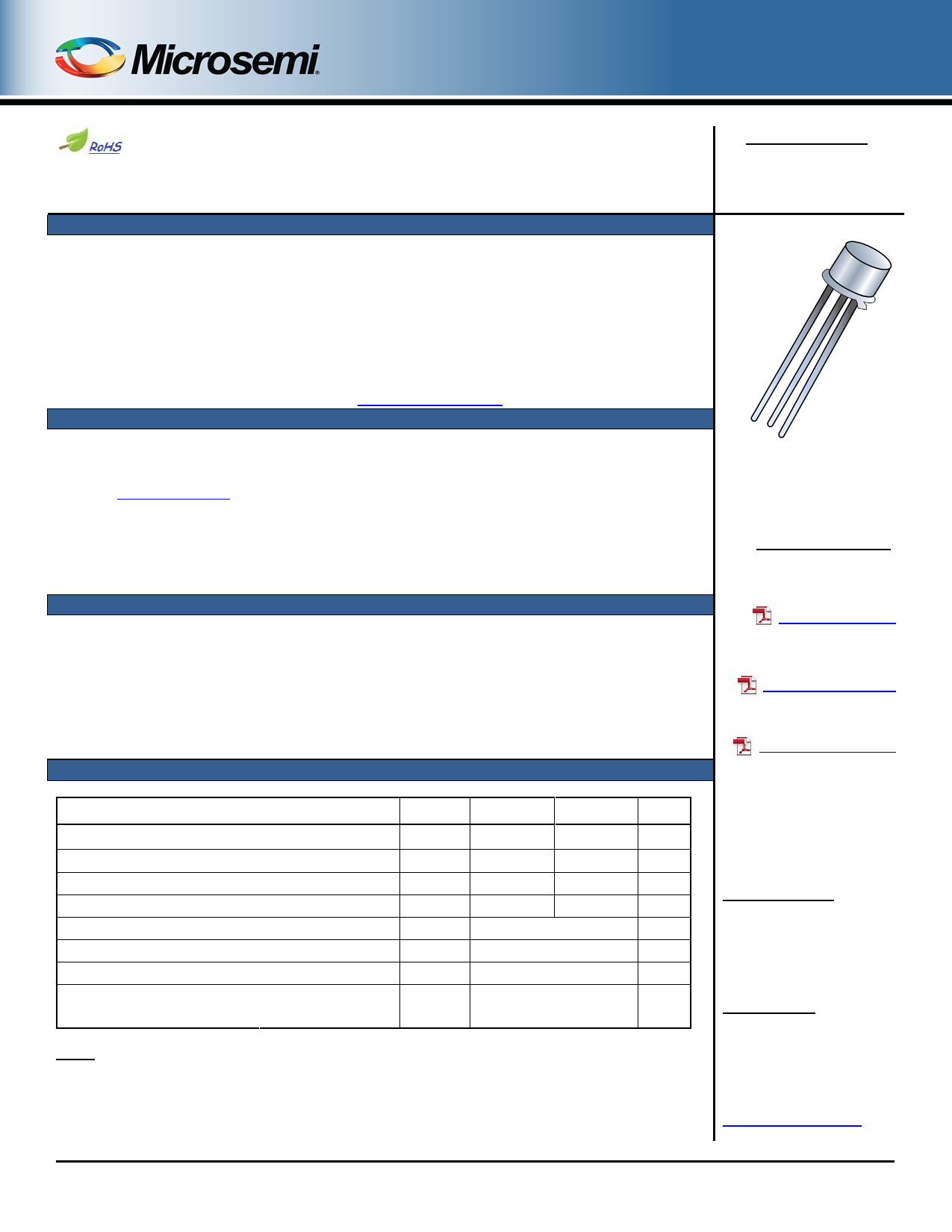

Time (s)

FIGURE 2

Thermal impedance graph (RӨJA)

©2013 Microsemi Corporation

Page 5 of 6