|

|

PDF A25LQ16 Data sheet ( Hoja de datos )

| Número de pieza | A25LQ16 | |

| Descripción | Dual/Quad-I/O Serial Flash Memory | |

| Fabricantes | AMIC | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de A25LQ16 (archivo pdf) en la parte inferior de esta página. Total 30 Páginas | ||

|

No Preview Available !

A25LQ16 Series

16Mbit, 3V Suspend/Resume, Dual/Quad-I/O Serial Flash Memory

with 100MHz Uniform 4KB Sectors

Document Title

16Mbit, 3V Suspend/Resume, Dual/Quad-I/O Serial Flash Memory with 100MHz Uniform

4KB Sectors

Revision History

Rev. No.

0.0

1.0

1.1

1.2

History

Initial issue

Final version release

Change tSE(typ.) from 150ms to 0.08s

Change tSE(max.) from 280ms to 0.2s

Change tBE(typ,) from 0.7s to 0.5s

P50: Change ICC6 & ICC7(max.) from 15mA to 25mA

Issue Date

August 17, 2011

August 29, 2011

November 15, 2011

Remark

Preliminary

Final

March 29, 2012

(March, 2012, Version 1.2)

AMIC Technology Corp.

1 page

SPI MODES

These devices can be driven by a microcontroller with its SPI

peripheral running in either of the two following modes:

– CPOL=0, CPHA=0

– CPOL=1, CPHA=1

For these two modes, input data is latched in on the rising

edge of Serial Clock (C), and output data is available from the

A25LQ16 Series

falling edge of Serial Clock (C).

The difference between the two modes, as shown in Figure 1,

is the clock polarity when the bus master is in Stand-by mode

and not transferring data:

– C remains at 0 for (CPOL=0, CPHA=0) Æ Mode 0

– C remains at 1 for (CPOL=1, CPHA=1) Æ Mode 3

Figure 1. SPI Modes Supported

CPOL CPHA

Mode 0 0

0C

Mode 3 1

1C

DIO

DO

MSB

MSB

(March, 2012, Version 1.2)

4 AMIC Technology Corp.

5 Page

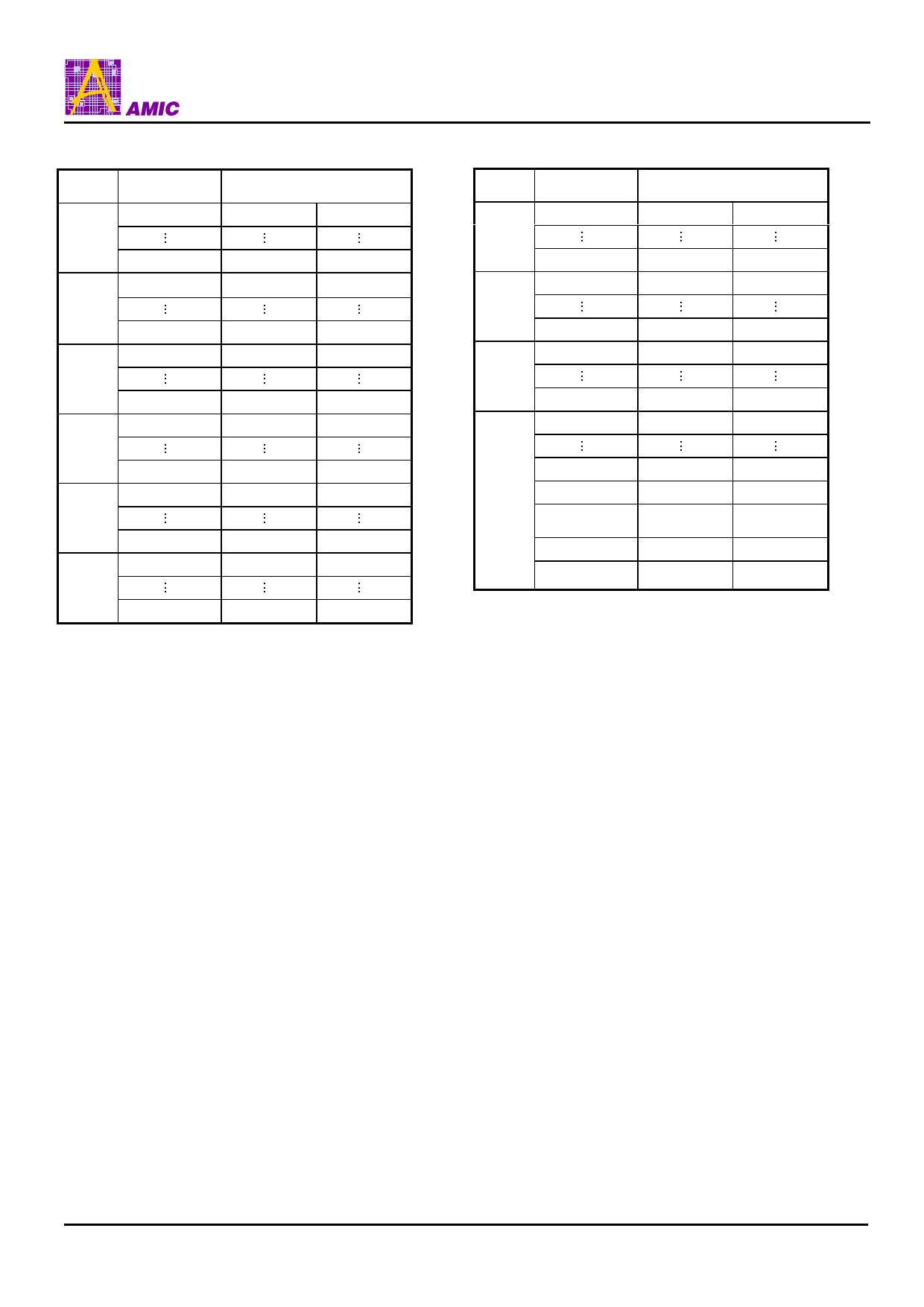

Memory Organization (Continued)

Block

9

8

Sector

159

144

143

Address range

9F000h

9FFFFh

90000h

8F000h

90FFFh

8FFFFh

128

80000h

80FFFh

127

7F000h

7FFFFh

7

112

70000h

70FFFh

111

6F000h

6FFFFh

6

96

60000h

60FFFh

95

5F000h

5FFFFh

5

80

50000h

50FFFh

79

4F000h

4FFFFh

4

64

40000h

40FFFh

A25LQ16 Series

Block

3

2

1

0

Sector

63

48

47

32

31

16

15

4

3

2

1

0

Address range

3F000h

3FFFFh

30000h

2F000h

30FFFh

2FFFFh

20000h

1F000h

20FFFh

1FFFFh

10000h

0F000h

10FFFh

0FFFFh

04000h

03000h

02000h

01000h

00000h

04FFFh

03FFFh

02FFFh

01FFFh

00FFFh

(March, 2012, Version 1.2)

10 AMIC Technology Corp.

11 Page | ||

| Páginas | Total 30 Páginas | |

| PDF Descargar | [ Datasheet A25LQ16.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| A25LQ16 | Dual/Quad-I/O Serial Flash Memory | AMIC |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |