|

|

PDF UJA1023T Data sheet ( Hoja de datos )

| Número de pieza | UJA1023T | |

| Descripción | LIN-I/O slave | |

| Fabricantes | NXP Semiconductors | |

| Logotipo | ||

Hay una vista previa y un enlace de descarga de UJA1023T (archivo pdf) en la parte inferior de esta página. Total 30 Páginas | ||

|

No Preview Available !

UJA1023

LIN-I/O slave

Rev. 5 — 17 August 2010

Product data sheet

1. General description

The UJA1023 is a stand-alone Local Interconnect Network (LIN) I/O slave that replaces

basic components commonly used in electronic control units for input and output handling.

The UJA1023 contains a LIN 2.0 controller, an integrated LIN transceiver which is

LIN 2.0 / SAE J2602 compliant and LIN 1.3 compatible, a 30 kΩ termination resistor

necessary for LIN-slaves, and eight I/O ports which are configurable via the LIN bus.

An automatic bit rate synchronization circuit adapts to any (master) bit rate between

1 kbit/s and 20 kbit/s. For this, an oscillator is integrated.

The LIN protocol will be handled autonomously and both Node Address (NAD) and LIN

frame Identifier (ID) programming will be done by a master request and an optional slave

response message in combination with a daisy chain or plug coding function.

The eight bidirectional I/O pins are configurable via LIN bus messages and can have the

following functions:

• Input:

– Standard input pin

– Local wake-up

– Edge capturing on falling, rising or both edges

– Analog input pin

– Switch matrix (in combination with output pins)

• Output:

– Standard output pin as high-side driver, low-side driver or push-pull driver

– Cyclic sense mode for local wake-up

– Pulse Width Modulation (PWM) mode; for example, for back light illumination

– Switch matrix (in combination with input pins)

On entering a low-power mode it is possible to hold the last output state or to change over

to a user programmable output state. In case of a failure (e.g. LIN bus short to ground) the

output changes over to a user programmable limp home output state and the low-power

Limp home mode will be entered.

Due to the advanced low-power behavior the power consumption of the UJA1023 in

low-power mode is minimal.

1 page

NXP Semiconductors

UJA1023

LIN-I/O slave

7. Functional description

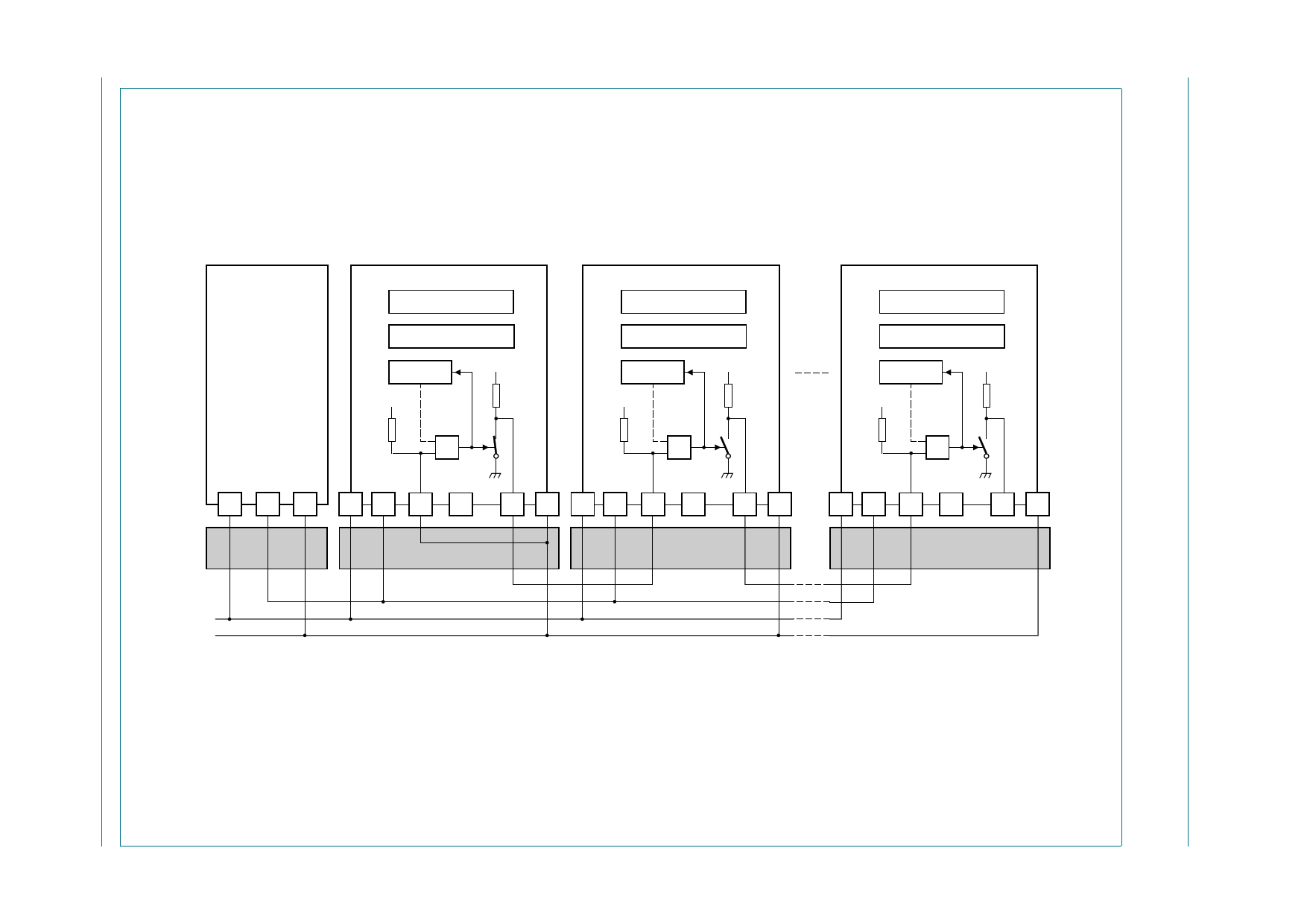

The UJA1023 combines all blocks necessary to work as a stand-alone LIN slave. Various

I/O functions typically used in a car are supported. For a more detailed description refer to

Section 7.2 to Section 7.6. The block diagram is shown in Figure 1.

7.1 Short description of the UJA1023

7.1.1 LIN controller

The LIN 2.0 controller monitors and evaluates the LIN messages in order to process the

LIN commands. It supervises and executes the NAD assignment, ID assignment and

I/O-configuration and controls the operating modes of the UJA1023.

The NAD configuration is done by a combination of a LIN master request frame and a

setting done by either a daisy chain or plug ID code.

7.1.2 LIN transceiver (including termination)

The LIN transceiver, which is LIN 2.0 / SAE J2602 compliant, is the interface between the

internal LIN controller and the physical LIN bus. The transmit data stream of the LIN

controller is converted into a bus signal with an optimized wave shape to minimize

electromagnetic emission. The required LIN slave termination of 30 kΩ is already

integrated. In case of LIN bus faults the UJA1023 switches to the low-power Limp home

mode.

7.1.3 Automatic bit rate detection

The automatic bit rate detection adapts to the LIN master’s bit rate. Any bit rate between

1 kbit/s and 20 kbit/s can be handled. This block checks whether the synchronization

break and synchronization field are valid. If not, the message will be rejected.

7.1.4 Oscillator

The on-chip oscillator provides the internal clock signal for some digital functions and is

the time reference for the automatic bit rate detection.

7.1.5 I/O block

The I/O block controls the configuration of the I/O pins. The LIN master configures the I/O

pin functionality by means of a master request frame and an optional slave response

frame.

Besides the standard level input and output behavior the following functions are also

handled by the UJA1023: local wake-up, cyclic input, edge capture, PWM output, switch

matrix I/O and AD conversion.

7.1.6 ADC

With three external components an 8-bit ADC function can be implemented. Each of the

eight bidirectional I/O pins can be used as input for the ADC, one at a time.

7.1.7 PWM

Each pin can be configured with a Pulse Width Modulation (PWM) function. The resolution

is 8-bit and the base frequency is approximately 2.7 kHz.

UJA1023

Product data sheet

All information provided in this document is subject to legal disclaimers.

Rev. 5 — 17 August 2010

© NXP B.V. 2010. All rights reserved.

5 of 49

5 Page

xxxxxxxxxxxxxxxxxxxxx xxxxxxxxxxxxxxxxxxxxxxxxxx xxxxxxx x x x xxxxxxxxxxxxxxxxxxxxxxxxxxxxxx xxxxxxxxxxxxxxxxxxx xx xx xxxxx

xxxxxxxxxxxxxxxxxxxxxxxxxxx xxxxxxxxxxxxxxxxxxx xxxxxx xxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxx xxxxxxxxxxxx x x

xxxxxxxxxxxxxxxxxxxxx xxxxxxxxxxxxxxxxxxxxxxxxxxxxxx xxxxx xxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxx xxxxxxxx

xxxxxxxxxxxxxxxxxxxxxxxxx xxxxxxxxxxxxxxxxxxxx xxx

MASTER

CONFIGURED

UJA1023

ASSIGN NAD

1

INITIAL NAD = DAISY CHAIN

DC FLAG

BAT

BAT

&

IN CONFIGURATION

UJA1023

ASSIGN NAD

2

INITIAL NAD = DAISY CHAIN

DC FLAG

BAT

BAT

&

NOT CONFIGURED

UJA1023

ASSIGN NAD

n

INITIAL NAD = DAISY CHAIN

DC FLAG

BAT

BAT

&

BAT LIN GND

BAT LIN

C1

C2

C3 GND BAT LIN

C1

C2

C3 GND

BAT LIN C1

C2

C3 GND

PLUG

PLUG

PLUG

PLUG

BAT

GND

mdb492

Fig 4. Daisy chain ID

11 Page | ||

| Páginas | Total 30 Páginas | |

| PDF Descargar | [ Datasheet UJA1023T.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| UJA1023 | LIN-I/O slave | NXP Semiconductors |

| UJA1023T | LIN-I/O slave | NXP Semiconductors |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |