|

|

PDF WM8962 Data sheet ( Hoja de datos )

| Número de pieza | WM8962 | |

| Descripción | Ultra-Low Power Stereo CODEC | |

| Fabricantes | Cirrus Logic | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de WM8962 (archivo pdf) en la parte inferior de esta página. Total 30 Páginas | ||

|

No Preview Available !

WM8962

Ultra-Low Power Stereo CODEC with

Audio Enhancement DSP, 1W Stereo Class D Speaker Drivers

and Ground Referenced Headphone Drivers

DESCRIPTION

FEATURES

The WM8962 is a low power, high performance stereo CODEC

designed for portable digital audio applications.

An integrated charge pump provides a ground referenced output

which removes the need for DC-blocking capacitors on the

headphone outputs, and uses the Wolfson ‘Class-W’ amplifier

techniques - incorporating an innovative dual-mode charge

pump architecture - to optimise efficiency and power

consumption during playback. A DC Servo is used to reduce DC

ground offsets. This improves power consumption and

minimises pops and clicks.

Stereo class D speaker drivers provide 1W per channel into 8

loads, or 2W mono into a 4 load, with a 5V supply. Low

leakage, excellent PSRR and pop/click suppression

mechanisms also allow direct battery connection to the speaker

supply. Flexible speaker boost settings allow speaker output

power to be maximised while minimising other analogue supply

currents.

Control sequences for audio path setup can be pre-loaded and

executed by an integrated sequencer to reduce software driver

development and eliminate pops and clicks via SilentSwitch™

technology.

Flexible input configuration: four stereo inputs or eight mono

inputs on Left or Right ADC, with a complete analogue (four

single-ended stereo inputs) and digital microphone interface.

External component requirements are drastically reduced as no

separate microphone, speaker or headphone amplifiers are

required. Advanced on-chip digital signal processing performs

automatic level control for the microphone or line input.

Stereo 24-bit sigma-delta ADCs and DACs are used with low

power over-sampling digital interpolation and decimation filters

and a flexible digital audio interface.

A programmable audio enhancement DSP is included with

multiple preset algorithms. Virtual Surround Sound widens the

stereo speaker audio image, HD Bass enhances low

frequencies, and ReTuneTM flattens the frequency response of

the speaker or microphone path. A configurable DSP includes

additional functions such as 3D widening for recording, a 5-band

parametric EQ and Dynamic Range Controller.

Two high performance PLLs and one Frequency Locked Loop

(FLL) are integrated to enable the user to clock a full audio

system.

The WM8962 operates at analogue supply voltages down to

1.7V, although the digital supplies can operate at voltages down

to 1.62V to save power. The speaker supply can operate at up

to 5.5V. Unused functions can be disabled using software

control to save power.

The WM8962 is supplied in a very small W-CSP package, ideal

for use in hand-held and portable systems.

DAC SNR 98dB (‘A’ weighted), THD -84dB at 48kHz, 1.8V

ADC SNR 94dB (‘A’ weighted), THD -85dB at 48kHz, 1.8V

Stereo Class D Speaker Driver

- 1W per channel into 8 BTL speakers

- 2W mono into 4 BTL speakers

- Flexible internal switching clock

Wolfson ‘Class-W’ ultra-low power headphone driver

- Up to 31mW per channel output power at 1% THD+N

into 16 at 1.8V

- Ground Referenced

- Low offset (+/- 1.2mV)

- Pop and click suppression

- Control sequencer for pop-minimised power-up/down

- Single register write for default start-up sequence

Microphone Interface

- Single ended four stereo analogue input

- Integrated low noise MICBIAS

- Digital microphone interface

- Programmable ALC / Limiter and Noise Gate

Programmable Audio Enhancement DSP with Presets

- Virtual Surround Sound

- HD Bass

- ReTuneTM

Fixed Audio Processing DSP

- 3D stereo widening

- 5-band Parametric EQ

- Dynamic range controller

- Beep generator

Two integrated PLLs enable clocking of full audio system

Low Power Consumption

- 7.7mW headphone playback

- 8.3mW analogue record mode

Low Supply Voltages

- Analogue 1.7V to 2.0V (Speaker supply up to 5.5V)

- Charge pump 1.7V to 2.0V

- MIC bias amp supply 1.7V to 3.6V

- Digital 1.62V to 2.0V

2-wire I2C and 3- or 4-wire SPI serial control interface

Standard sample rates from 8kHz to 96kHz

W-CSP, 3.6x3.9mm 49-pin

APPLICATIONS

Portable gaming, Voice recorders

Mobile multimedia

Stereo DSC-Camcorder

http://www.cirrus.com

Copyright Cirrus Logic, Inc., 2009–2015

(All Rights Reserved)

Rev 4.3

JUN ‘15

1 page

WM8962

DIGITAL AUDIO INTERFACE .................................................................................... 138

MASTER AND SLAVE MODE OPERATION ...........................................................................................139

OPERATION WITH TDM.........................................................................................................................139

BCLK FREQUENCY ................................................................................................................................140

AUDIO DATA FORMATS (NORMAL MODE) ..........................................................................................140

AUDIO DATA FORMATS (TDM MODE)..................................................................................................142

DIGITAL AUDIO INTERFACE CONTROL.................................................................. 144

AUDIO INTERFACE TRI-STATE.............................................................................................................145

BCLK AND LRCLK CONTROL................................................................................................................145

COMPANDING ........................................................................................................................................146

LOOPBACK .............................................................................................................................................148

CLOCKING AND SAMPLE RATES ............................................................................ 149

SYSCLK CONTROL ................................................................................................................................150

AUTOMATIC CLOCKING CONFIGURATION .........................................................................................152

DSP, ADC, DAC CLOCK CONTROL.......................................................................................................154

CLASS D, 256K, DC SERVO CLOCK CONTROL...................................................................................155

OPCLK CONTROL ..................................................................................................................................156

TOCLK, DBCLK CONTROL ....................................................................................................................156

BCLK AND LRCLK CONTROL................................................................................................................157

CONTROL INTERFACE CLOCKING ......................................................................................................157

INTERNAL / EXTERNAL CLOCK GENERATION ...................................................... 158

START-UP OPTIONS FOR INTERNAL / EXTERNAL CLOCK GENERATION.......................................159

INTERNAL OSCILLATOR CONTROL .....................................................................................................160

CLKOUT CONTROL................................................................................................................................162

FREQUENCY LOCKED LOOP (FLL) ......................................................................................................164

FREE-RUNNING FLL CLOCK.................................................................................................................168

EXAMPLE FLL CALCULATION...............................................................................................................169

PHASE LOCKED LOOP (PLL) ................................................................................................................170

EXAMPLE PLL CALCULATION ..............................................................................................................174

GENERAL PURPOSE INPUT/OUTPUT (GPIO)......................................................... 175

INTERRUPTS ............................................................................................................ 179

CONTROL INTERFACE............................................................................................. 184

SELECTION OF CONTROL INTERFACE MODE ...................................................................................184

2-WIRE (I2C) CONTROL MODE .............................................................................................................185

3-WIRE (SPI) CONTROL MODE .............................................................................................................188

4-WIRE (SPI) CONTROL MODE .............................................................................................................189

CONTROL WRITE SEQUENCER .............................................................................. 190

INITIATING A SEQUENCE......................................................................................................................190

PROGRAMMING A SEQUENCE ............................................................................................................191

DEFAULT SEQUENCES .........................................................................................................................194

THERMAL SHUTDOWN ............................................................................................ 198

SOFTWARE RESET AND CHIP ID............................................................................ 199

REGISTER MAP ................................................................................................ 200

REGISTER BITS BY ADDRESS ................................................................................ 209

DIGITAL FILTER CHARACTERISTICS ............................................................ 274

DAC FILTER RESPONSES ....................................................................................... 275

ADC FILTER RESPONSES ....................................................................................... 277

ADC HIGH PASS FILTER RESPONSES ................................................................................................278

DE-EMPHASIS FILTER RESPONSES....................................................................... 279

APPLICATIONS INFORMATION ...................................................................... 280

ANALOGUE INPUT PATHS ....................................................................................................................280

MICROPHONE BIAS CIRCUIT ...............................................................................................................280

CHARGE PUMP COMPONENTS ...........................................................................................................282

RECOMMENDED EXTERNAL COMPONENTS DIAGRAM....................................................................283

Rev 4.3

5

5 Page

WM8962

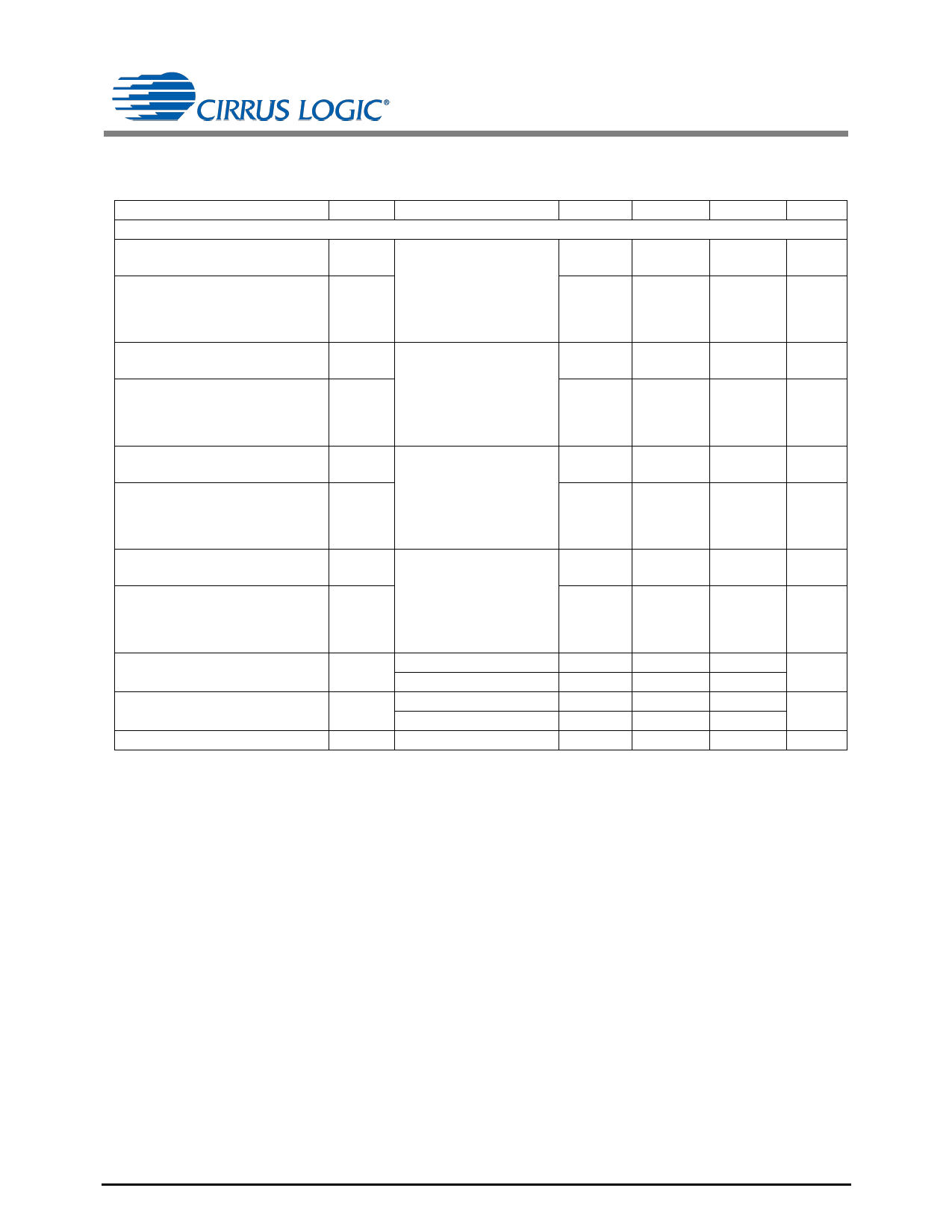

Test Conditions

MICVDD = DCVDD = DBVDD = CPVDD = AVDD = PLLVDD = 1.8V, SPKVDD1 = SPKVDD2 = 5V.

TA = +25oC, 1kHz signal, fs = 48kHz, PGA gain = 0dB, 24-bit audio data unless otherwise stated.

PARAMETER

SYMBOL TEST CONDITIONS

MIN

Analogue Inputs (IN1L, IN1R) to ADC out via Input PGA and Input Gain Boost

Signal to Noise Ratio

(A-weighted)

Total Harmonic Distortion Plus

Noise (-1dBFS input)

SNR

THD+N

ADC_HP=0

MIXIN_BIAS=100

INPGA_BIAS=100

‘Option 1’ (low power) bias

settings - see Note 2.

Signal to Noise Ratio

(A-weighted)

Total Harmonic Distortion Plus

Noise (-1dBFS input)

SNR

THD+N

ADC_HP=0

MIXIN_BIAS=011

INPGA_BIAS=100

‘Option 2’ bias settings -

see Note 2.

Signal to Noise Ratio

(A-weighted)

Total Harmonic Distortion Plus

Noise (-1dBFS input)

SNR

THD+N

ADC_HP=0

MIXIN_BIAS=000

INPGA_BIAS=100

‘Option 3’ bias settings -

see Note 2.

81

Signal to Noise Ratio

(A-weighted)

Total Harmonic Distortion Plus

Noise (-1dBFS input)

SNR

THD+N

ADC_HP=1

MIXIN_BIAS=000

INPGA_BIAS=000

‘Option 4’ (high performance)

bias settings - see Note 2.

ADC Channel Separation

1kHz

10kHz

PSRR (AVDD)

100mV(peak-peak) 1kHz

100mV(peak-peak) 20kHz

Channel Matching

1kHz signal

TYP

91

-70

91

-75

91

-82

93

-82

95

97

60

40

+/-0.5

MAX

UNIT

dB

dB

dB

dB

dB

-72 dB

dB

dB

dB

dB

dB

Rev 4.3

11

11 Page | ||

| Páginas | Total 30 Páginas | |

| PDF Descargar | [ Datasheet WM8962.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| WM8960 | Stereo CODEC | Wolfson Microelectronics |

| WM8961 | Ultra-Low Power Stereo CODEC | Wolfson Microelectronics |

| WM8962 | Ultra-Low Power Stereo CODEC | Wolfson Microelectronics |

| WM8962 | Ultra-Low Power Stereo CODEC | Cirrus Logic |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |